## High-Performance Data Converters

by

Jesper Steensgaard-Madsen (Steensgaard@ieee.org)

A thesis submitted in partial fulfillment of the requirementments for the Ph.D. degree

The Technical University of Denmark

Department of Information Technology

DK-2800, Lyngby Denmark

January 20, 1999 (Revised March 8, 1999)

© by Jesper Steensgaard-Madsen, 1999

Copyright ©

by Jesper Steensgaard-Madsen, 1999

All rights reserved

### **Abstract**

Novel techniques for multi-bit oversampled data conversion are described. State-of-the-art oversampled data converters are analyzed, leading to the conclusion that their performance is limited mainly by low-resolution signal representation. To increase the resolution, high-performance, high-resolution internal D/A converters are required. Unit-element mismatch-shaping D/A converters are analyzed, and the concept of mismatch-shaping is generalized to include scaled-element D/A converters. Several types of scaled-element mismatch-shaping D/A converters are proposed. Simulations show that, when implemented in a standard CMOS technology, they can be designed to yield 100 dB performance at 10 times oversampling.

The proposed scaled-element mismatch-shaping D/A converters are well suited for use as the feedback stage in oversampled delta-sigma quantizers. It is, however, not easy to make full use of their potential, because that requires a high-resolution loop quantizer which introduces only a small delay. Generally, it is not acceptable to design the loop quantizer as a high-resolution flash quantizer because they require a large chip area and high power consumption. Pipeline techniques are proposed to circumvent this problem. This way, the delta-sigma quantizer's feedback signal is obtained by a multiple-stage quantization, where the loop quantizer (low-resolution and minimum-delay) implements only the last-stage quantization. Hence, high-speed, high-resolution delta-sigma quantization is feasible without using complex circuitry.

An improved version of the MASH topology is also proposed. A delta-sigma quantizer is used to quantize the input signal into an oversampled digital representation of low-to-moderate resolution. The delta-

sigma quantizer's truncation error is estimated either directly, or as the first-order difference of the output signal from the loop filter's first integrator stage. This technique avoids the need for accurate matching of analog and digital filters that characterizes the MASH topology, and it preserves the signal-band suppression of quantization errors. Simulations show that quantizers of this type can yield 100 dB performance at 10 times oversampling. There are no requirements for high-resolution flash quantizers or other hard-to-implement circuitry.

## Acknowledgements

The author wishes to acknowledge several people for their contributions to this work.

In a category by himself, Professor Gabor C. Temes has helped me in countless ways during the almost two years I have been fortunate enough to work with him. I thank him for his friendship, encouragement, advice, enthusiasm, ideas, feedback, editing, our discussions, and for providing an environment where electrical engineering can be practiced in a fun and rewarding way. He truly deserves the "IEEE Graduate Teaching Award," which was awarded to him in 1998. He has my highest respect and appreciation in every aspect.

At Oregon State University I have worked with many wonderful people with whom I have had fruitful discussions. They have included Professor Un-Ku Moon, Professor Richard Schreier, Luis Hernandez, Andreas Wiesbauer, Paul Ferguson, Yunteng Huang, Bo Wang, Tao Sun, and many more.

I particularly wish to thank the President of MEAD Microelectronics Inc. of Switzerland, Vlado Valence, and Gabor and Ibi Temes, from U.S. MEAD, for inviting me to participate in the outstanding courses in electrical engineering which they arrange in Switzerland and in the United States. I believe I have obtained some of my most useful and practical information from these courses, and I am very grateful for that. I need to thank the outstanding course lecturers who teach these courses, many of whom I have been fortunate to encounter in private and fruitful discussions. In arbitrary order, I particularly wish to thank Bob Adams, Eric Vittoz, Paul Brokaw, Tim Schmerbeck, Christian Enz, Todd Brooks, Paul Ferguson, Bob Blauschild, Ian Galton, Berrie Gilbert, Stephen Jantzi and several others.

I also extend my thanks to the design team at MEAD Microelectronics Inc., particularly Fabien and Phillip Duval.

For making my life pleasant in many ways, I wish to thank my brother, Bjarne, his wife, Tamara, and my girlfriend, Patrice. Also, I wish to thank Ms. Ibi Temes for her gracious hospitality at the Temes' home on several occasions.

Finally, I wish to thank my supervisor, Erik Bruun, and the Danish educational system for its financial support.

## **Contents**

| 1 | Intr | oduction 1 |                                                   |    |  |  |  |

|---|------|------------|---------------------------------------------------|----|--|--|--|

|   | 1.1  | The C      | lass of Data Converters Considered                | 3  |  |  |  |

|   | 1.2  | The St     | ructure of This Thesis                            | 6  |  |  |  |

|   | 1.3  | Intelle    | ctual Property Rights                             | 7  |  |  |  |

| 2 | Cha  | racteriz   | zation of Signals                                 | 9  |  |  |  |

|   | 2.1  | Time-l     | Domain Representation of Signals                  | 9  |  |  |  |

|   |      | 2.1.1      | Analog Signals                                    | 10 |  |  |  |

|   |      | 2.1.2      | Digital Signals                                   | 11 |  |  |  |

|   | 2.2  | Freque     | ency-Domain Representation of Signals             | 12 |  |  |  |

|   |      | 2.2.1      | Fourier Transformation of Continuous-Time Signals | 13 |  |  |  |

|   |      | 2.2.2      | Fourier Transformation of Discrete-Time Signals   | 14 |  |  |  |

|   |      | 2.2.3      | Definition of the Signal Band                     | 16 |  |  |  |

|   |      | 2.2.4      | Nyquist's Sampling Theorem                        | 17 |  |  |  |

|   |      | 2.2.5      | Aliasing                                          | 18 |  |  |  |

vi CONTENTS

|   | 2.3  | Estima  | ation of a Signal's Fourier Spectrum         | 18 |

|---|------|---------|----------------------------------------------|----|

|   |      | 2.3.1   | Estimation Based on a Finite-Duration Signal | 19 |

|   |      | 2.3.2   | Estimation Based on Assumed Periodicity      | 21 |

|   |      | 2.3.3   | The Discrete Fourier Transformation          | 23 |

| 3 | Basi | c Aspec | ets of Data Conversion                       | 29 |

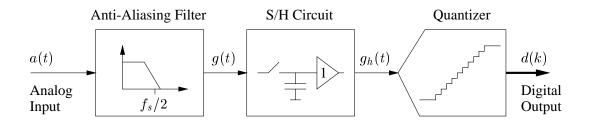

|   | 3.1  | Funda   | mental Steps in A/D Conversion               | 29 |

|   |      | 3.1.1   | Errors Caused by the Anti-Aliasing Filter    | 30 |

|   |      | 3.1.2   | Errors Caused by the Sample-and-Hold Circuit | 33 |

|   |      | 3.1.3   | Characterization of the Ideal Quantizer      | 35 |

|   |      | 3.1.4   | Characterization of Quantizer Errors         | 39 |

|   | 3.2  | Funda   | mental Steps in D/A Conversion               | 42 |

|   |      | 3.2.1   | Basic Voltage-Mode Implementation            | 42 |

|   |      | 3.2.2   | Basic Current-Mode Implementation            | 45 |

|   |      | 3.2.3   | Clock Jitter in D/A Converters               | 49 |

|   |      | 3.2.4   | Static Performance of D/A Converters         | 53 |

|   |      | 3.2.5   | Linearity Limitations                        | 55 |

|   | 3.3  | Measu   | ring Dynamic Performance                     | 60 |

|   |      | 3.3.1   | Signal-to-Noise Ratio                        | 61 |

|   |      | 3.3.2   | Dynamic Range                                | 61 |

|   |      | 3.3.3   | Spurious-Free Dynamic Range                  | 62 |

*CONTENTS* vii

|   |       | 3.3.4    | Intermodulation Distortion                        | 62         |

|---|-------|----------|---------------------------------------------------|------------|

|   | 3.4   | Quanti   | zer Topologies                                    | 62         |

|   |       | 3.4.1    | Direct-Comparison Data Quantizers                 | 63         |

|   |       | 3.4.2    | Residue-Calculating Data Quantizers               | 65         |

|   |       | 3.4.3    | Introduction to Signal Quantizers                 | 71         |

| 4 | State | e-of-the | -Art Signal Quantizers                            | <b>7</b> 9 |

|   | 4.1   | Single   | -Bit Delta-Sigma Quantizers                       | 80         |

|   |       | 4.1.1    | Obtaining and Preserving Stability                | 81         |

|   |       | 4.1.2    | Bandwidth Limitation                              | 86         |

|   | 4.2   | MASE     | I Topology                                        | 87         |

|   |       | 4.2.1    | Analysis of the MASH Topology                     | 88         |

|   | 4.3   | Multi-   | Bit Delta-Sigma Quantizers                        | 92         |

|   |       | 4.3.1    | Stability Properties                              | 93         |

|   | 4.4   | Misma    | atch-Shaping DACs                                 | 97         |

|   |       | 4.4.1    | Estimation of the Error Signal                    | 98         |

|   |       | 4.4.2    | First-Order Unit-Element Mismatch-Shaping DACs    | 100        |

|   |       | 4.4.3    | Performance of First-Order Mismatch-Shaping DACs  | 105        |

|   |       | 4.4.4    | Second-Order Mismatch-Shaping DACs                | 110        |

|   |       | 4.4.5    | Performance of Second-Order Mismatch-Shaping DACs | 116        |

|   |       | 4.4.6    | Mismatch-Shaping Encoders in Perspective          | 120        |

viii CONTENTS

|   | 4.5  | Noise Limitation                             |

|---|------|----------------------------------------------|

|   |      | 4.5.1 Discrete-Time Delta-Sigma Quantizers   |

|   |      | 4.5.2 Continuous-Time Delta-Sigma Quantizers |

|   |      | 4.5.3 Conclusion                             |

| 5 | Imp  | oved Current-Mode DACs 13.                   |

|   | 5.1  | Dual Return-to-Zero Current-Mode DAC         |

|   |      | 5.1.1 A Variation                            |

|   | 5.2  | Time-Interleaved Current-Mode DAC            |

|   |      | 5.2.1 Basic Topology and Operation           |

|   |      | 5.2.2 Analysis                               |

|   | 5.3  | Conclusion                                   |

| 6 | Dith | ring of Mismatch-Shaping DACs                |

|   | 6.1  | Idle Tones in Deterministic UE-MS Encoders   |

|   |      | 6.1.1 Idle Tones in ERS UE-MS Encoders       |

|   |      | 6.1.2 Idle Tones in Complex UE-MS Encoders   |

|   | 6.2  | Dithered UE-MS Encoders                      |

|   |      | 6.2.1 Dithered Tree-Structure UE-MS Encoders |

|   |      | 6.2.2 Dithered ERS UE-MS Encoders            |

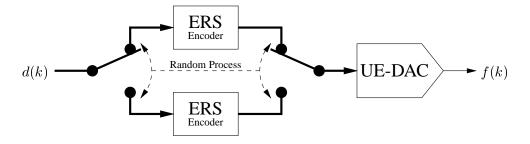

|   | 6.3  | Random-Orientation Dithered ERS Encoder      |

|   |      | 6.3.1 A Family of Dithering Techniques       |

*CONTENTS* ix

|   |      | 6.3.2   | Random-Rotation-Scheme Dithering                          | 160   |

|---|------|---------|-----------------------------------------------------------|-------|

|   | 6.4  | Conclu  | usion                                                     | 161   |

| 7 | Scal | ed-Elen | nent Mismatch-Shaping D/A Converters                      | 165   |

|   | 7.1  | High-I  | Resolution Mismatch-Shaping DACs                          | 166   |

|   |      | 7.1.1   | General Aspect of the Design of Mismatch-Shaping Encoders | . 166 |

|   |      | 7.1.2   | Mismatch-shaping Unit-Element DACs – Revisited            | 168   |

|   |      | 7.1.3   | Complicated Scaled-Element Mismatch-Shaping Encoders      | . 168 |

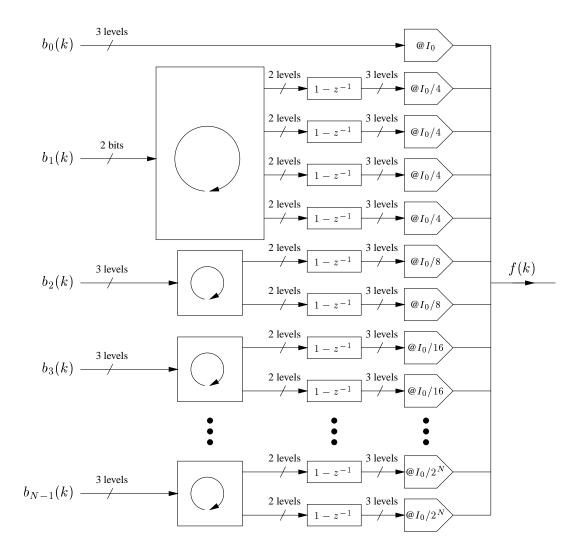

|   |      | 7.1.4   | Simple Scaled-Element Mismatch-Shaping Encoders           | . 169 |

|   | 7.2  | A Dua   | ıl-Type-Element Mismatch-Shaping DAC                      | 171   |

|   |      | 7.2.1   | Designing the Delta-Sigma Modulator                       | 172   |

|   |      | 7.2.2   | Parallel Work Published                                   | 174   |

|   | 7.3  | Tree-S  | Structure Scaled-Element Mismatch-Shaping DACs            | 176   |

|   |      | 7.3.1   | Asymmetrical Tree Structures                              | 178   |

|   |      | 7.3.2   | One-Sided Tree-Structure                                  | 180   |

|   | 7.4  | Filteri | ng Scaled-Element Mismatch-Shaping DACs                   | 182   |

|   |      | 7.4.1   | Minimalist Scaled-Element Mismatch-Shaping Encoder        | . 183 |

|   |      | 7.4.2   | Practical Filtering Scaled-Element Mismatch-Shaping DACs  | . 184 |

|   |      | 7.4.3   | Reducing the Gain-Error Sensitivity                       | 185   |

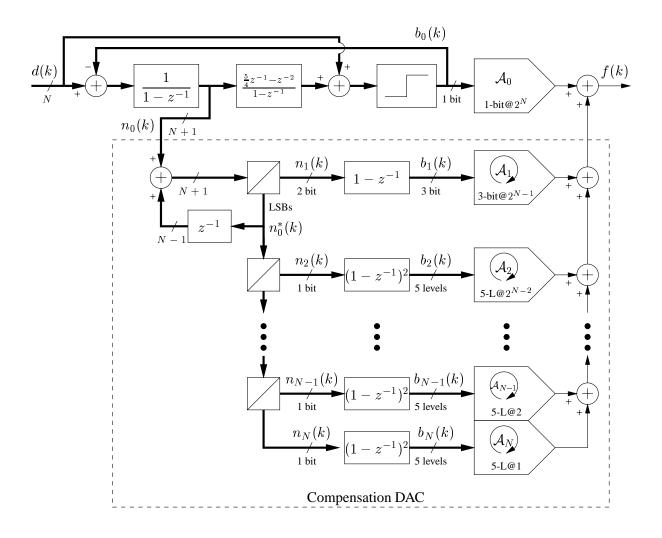

|   | 7.5  | Second  | d-Order Scaled-Element Mismatch-Shaping DACs              | 189   |

|   |      | 7.5.1   | The Generalized Filtering Principle                       | 189   |

X CONTENTS

|   |      | 7.5.2    | The Filter-Mismatch Problem                             | . 191 |

|---|------|----------|---------------------------------------------------------|-------|

|   |      | 7.5.3    | Variations                                              | . 192 |

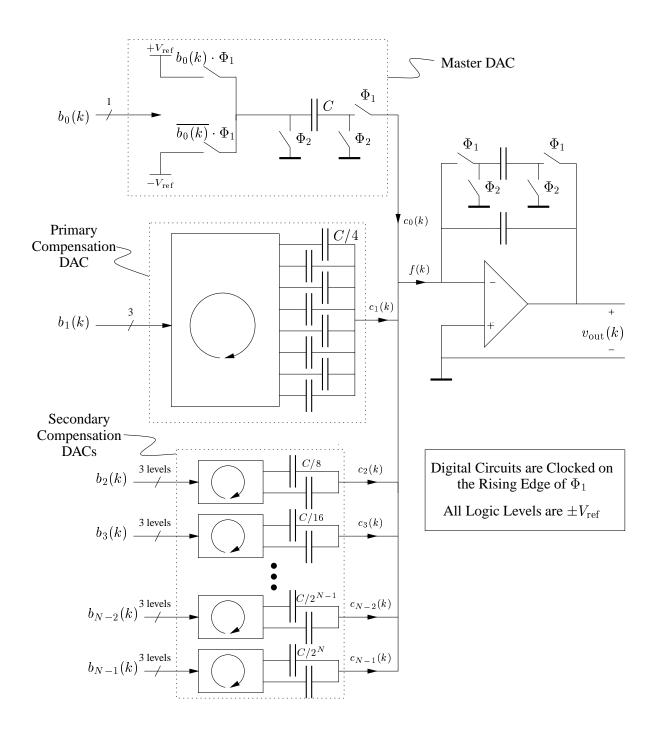

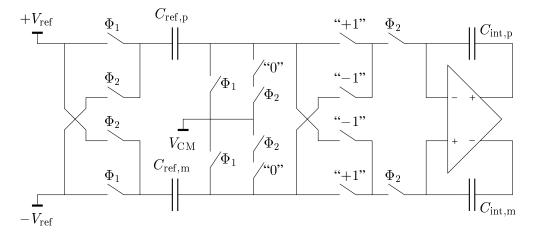

|   |      | 7.5.4    | Switched-Capacitor Implementation                       | . 193 |

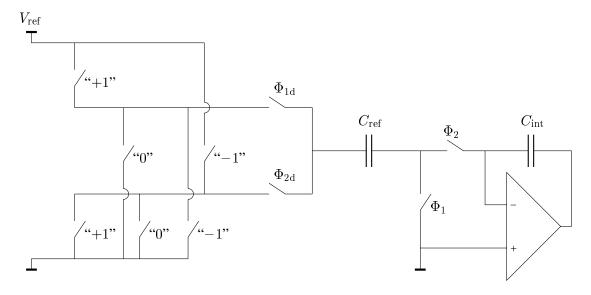

|   |      | 7.5.5    | Linear Three-Level DACs                                 | . 201 |

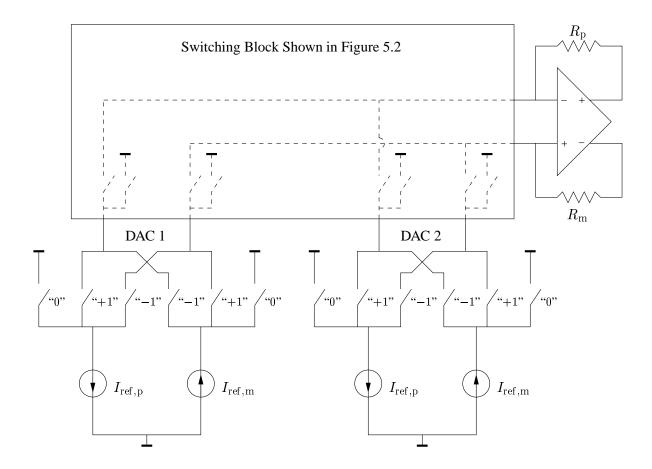

|   |      | 7.5.6    | Current-Mode Implementation                             | . 206 |

|   |      | 7.5.7    | Mismatch-Shaping Bandpass DACs                          | . 210 |

| 8 | Higl | h-Resolı | ution Delta-Sigma Quantizers                            | 211   |

|   | 8.1  | Choos    | ing the Optimal Resolution                              | . 212 |

|   |      | 8.1.1    | Fundamental Principle for High-Resolution Quantization  | . 213 |

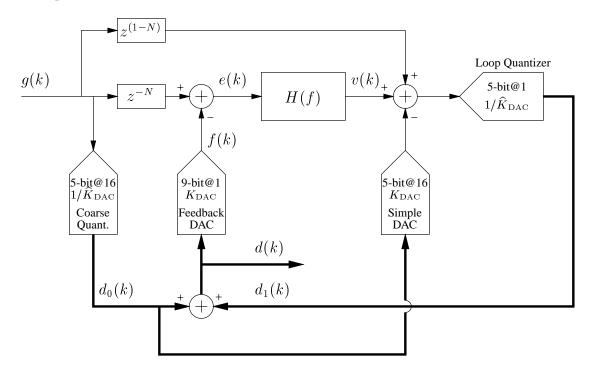

|   | 8.2  | Two-S    | tage Delta-Sigma Quantizers                             | . 213 |

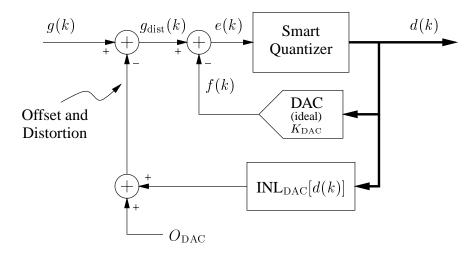

|   |      | 8.2.1    | Preventing Nonlinearity                                 | . 216 |

|   |      | 8.2.2    | Simulation Results                                      | . 217 |

|   | 8.3  | Impler   | mentation of Two-Stage Delta-Sigma Quantizers           | . 219 |

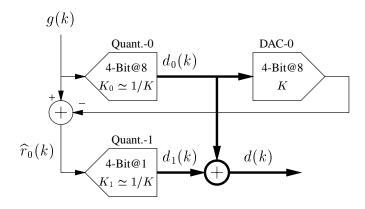

|   |      | 8.3.1    | Introducing Pipeline Techniques to Allow Circuit Delays | . 221 |

|   |      | 8.3.2    | Design of Analog Delay Lines                            | . 222 |

|   |      | 8.3.3    | Avoiding Sequential Settling                            | . 225 |

|   |      | 8.3.4    | Proposed Circuit-Level Implementation                   | . 226 |

| 9 | Resi | idue-Co  | mpensated Delta-Sigma Quantizers                        | 233   |

|   | 9.1  | Direct   | ly Residue-Compensated Delta-Sigma Quantizers           | . 234 |

|   |      | 9.1.1    | Analysis and Performance Evaluation                     | . 234 |

*CONTENTS* xi

| 10 Cor | nclusion |                                                               | 259   |

|--------|----------|---------------------------------------------------------------|-------|

|        | 9.3.3    | Conclusions                                                   | 257   |

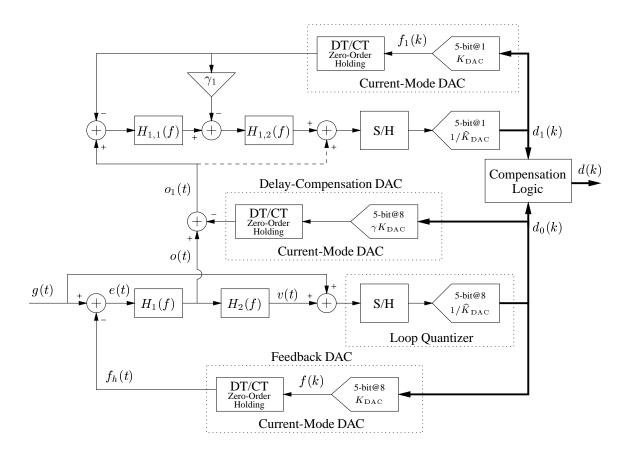

|        | 9.3.2    | Residue-Compensated Continuous-Time $\Delta\Sigma$ Quantizers |       |

|        | 9.3.1    | High-Resolution Continuous-Time Delta-Sigma Quantizers        | . 250 |

| 9.3    | Contin   | uous-Time Delta-Sigma Quantizers                              | . 250 |

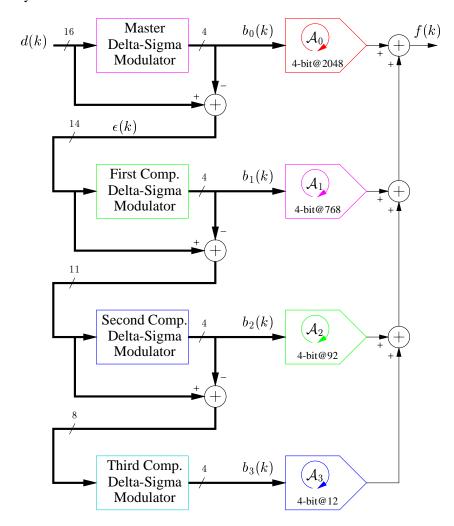

|        | 9.2.4    | Designing Residue-Compensated Delta-Sigma Quantizers          | . 248 |

|        | 9.2.3    | Controlling the Filter-Mismatch-Induced Error                 | . 244 |

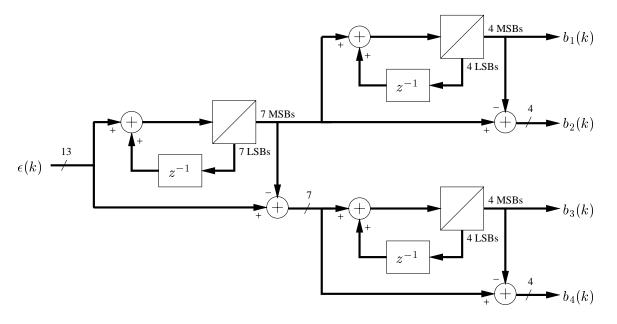

|        | 9.2.2    | Controlling the Residue-Quantization Error                    | . 239 |

|        | 9.2.1    | Analysis and Performance Evaluation                           | . 238 |

| 9.2    | Indirec  | ctly Residue-Compensated Delta-Sigma Quantizers               | . 236 |

xii CONTENTS

# **List of Figures**

| 2.1 | DT/CT conversions commonly used for signal analysis           | 15 |

|-----|---------------------------------------------------------------|----|

| 2.2 | A graphic interpretation of aliasing                          | 15 |

| 2.3 | The Fourier transform (magnitude) of the rectangular window   | 20 |

| 2.4 | The observed frequency spectrum of a two-tone periodic signal | 20 |

| 2.5 | Fundamental steps in the band-pass-filter method              | 22 |

| 2.6 | Examples of DTFs that are subject to spectral leakage         | 27 |

| 3.1 | Fundamental steps in A/D conversion                           | 30 |

| 3.2 | Aliasing errors                                               | 32 |

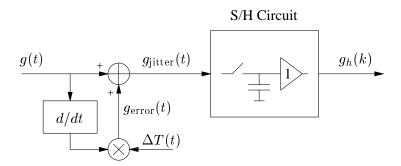

| 3.3 | Clock-jitter errors (sampling)                                | 35 |

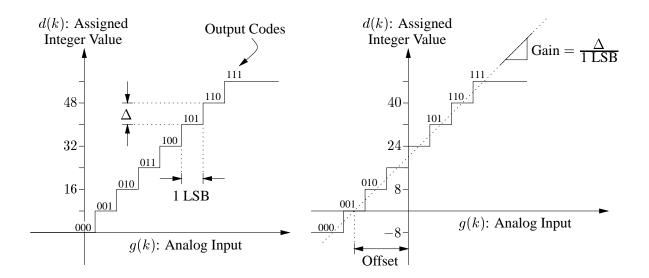

| 3.4 | Static characteristic for linear quantizers                   | 36 |

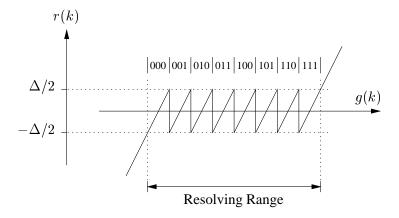

| 3.5 | Residue of an ideal quantizer                                 | 37 |

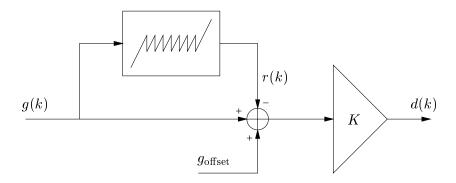

| 3.6 | Quantizer model                                               | 38 |

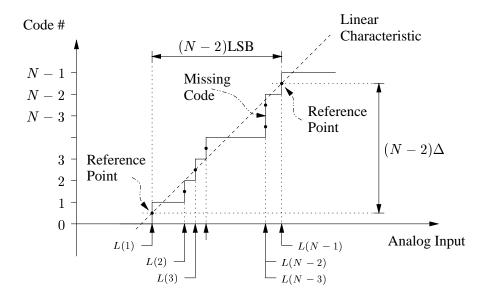

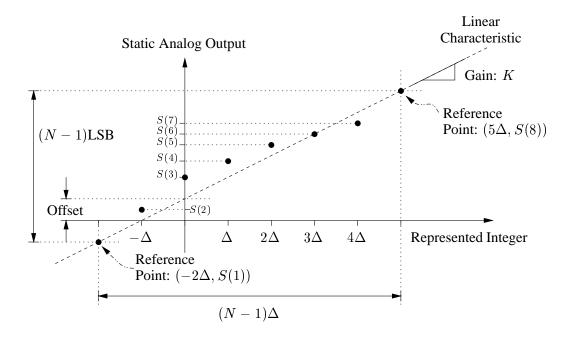

| 3.7 | Static characteristic of a nonideal quantizer                 | 39 |

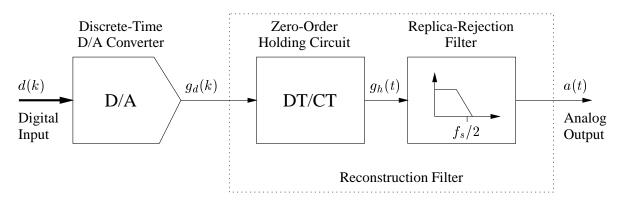

| 3.8 | Voltage-mode D/A converter system                             | 42 |

xiv LIST OF FIGURES

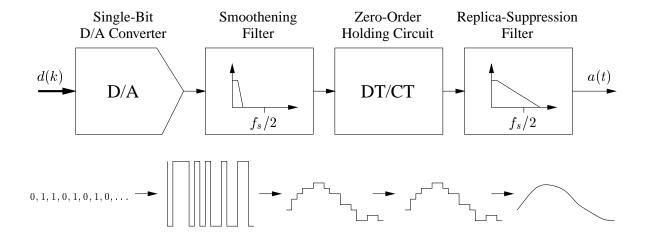

| 3.9  | Output stage of a single-bit delta-sigma D/A converter  | 44 |

|------|---------------------------------------------------------|----|

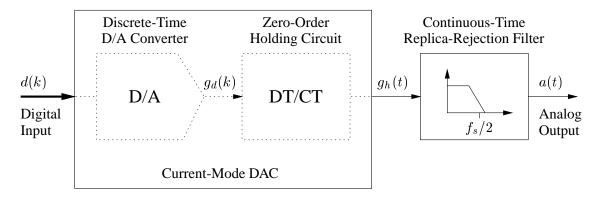

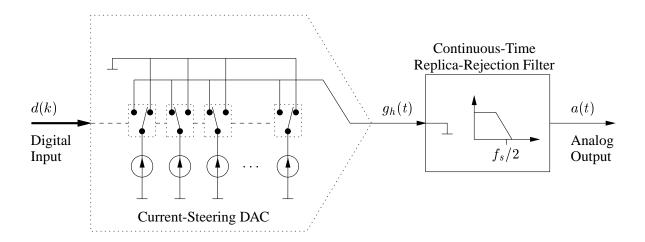

| 3.10 | Current-mode D/A converter system                       | 45 |

| 3.11 | Current-steering D/A converter                          | 46 |

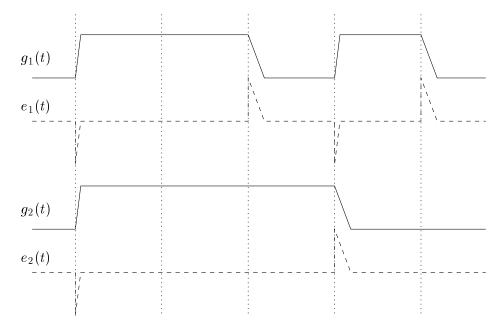

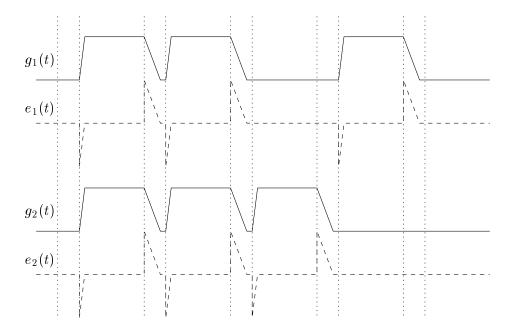

| 3.12 | Dynamic errors in a current-mode D/A converter          | 47 |

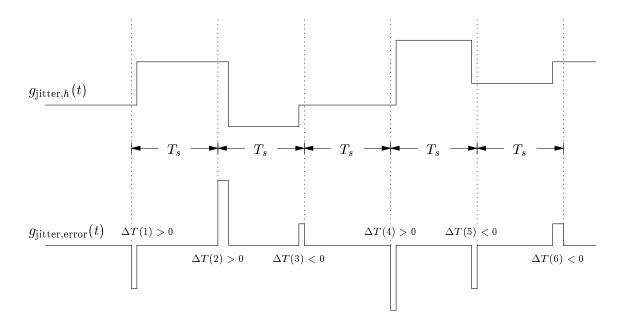

| 3.13 | Return-to-zero switching scheme                         | 49 |

| 3.14 | Clock jitter errors (reconstruction)                    | 50 |

| 3.15 | Static characteristic of an nonideal D/A converter      | 54 |

| 3.16 | Topology of most D/A converters                         | 55 |

| 3.17 | Basic residue stage                                     | 66 |

| 3.18 | Two-step flash quantizer                                | 67 |

| 3.19 | Scaled two-step flash quantizer                         | 68 |

| 3.20 | Four-stage pipeline quantizer                           | 70 |

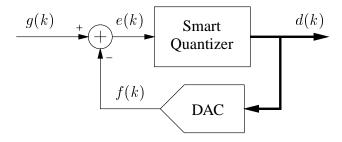

| 3.21 | Fundamental principle of signal quantizers              | 71 |

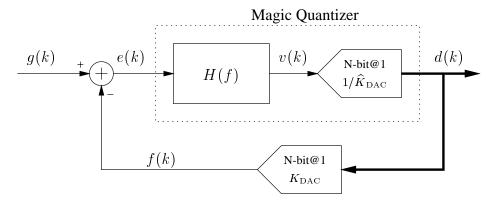

| 3.22 | Signal quantizer with a nonideal feedback D/A converter | 72 |

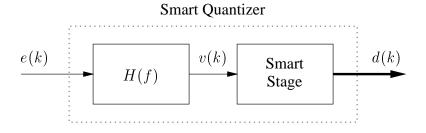

| 3.23 | Fundamental elements in a smart quantizer               | 74 |

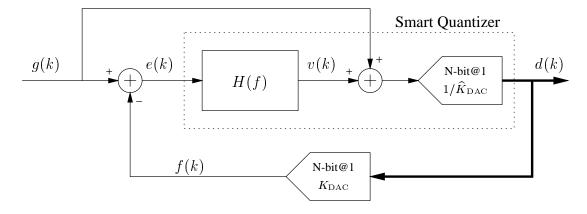

| 3.24 | Typical (delta-sigma) signal quantizer                  | 75 |

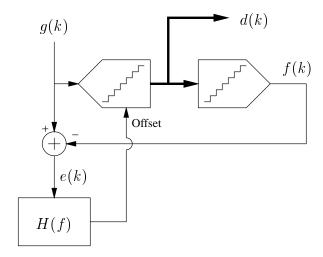

| 3.25 | Optimized (delta-sigma) signal quantizer                | 76 |

| 3.26 | Interpretation of (delta-sigma) signal quantizers       | 77 |

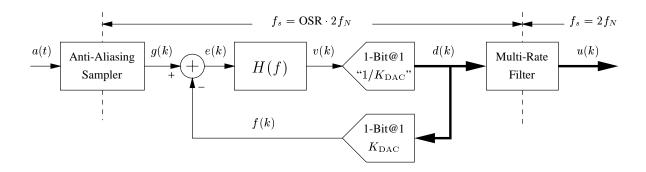

| 4.1  | Single-bit delta-sigma A/D converter system             | 81 |

|      |                                                         |    |

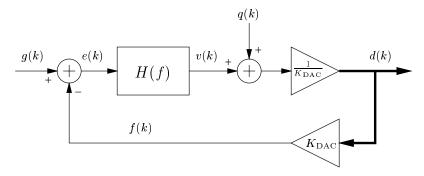

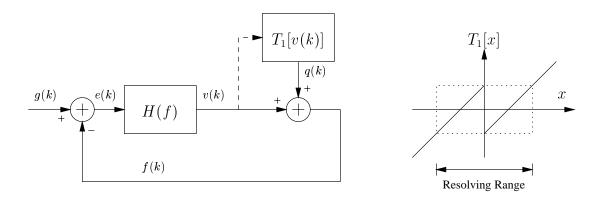

| 4.2  | Linear model of a delta-sigma loop                      | 82 |

LIST OF FIGURES xv

| 4.3  | Nonlinear model of a delta-sigma loop                         |

|------|---------------------------------------------------------------|

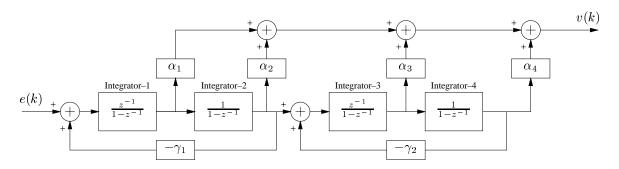

| 4.4  | Delta-sigma loop filter                                       |

| 4.5  | MASH-topology delta-sigma quantizer                           |

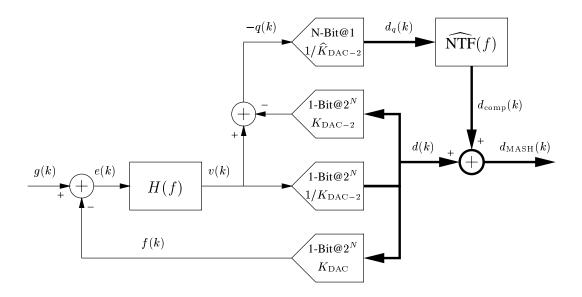

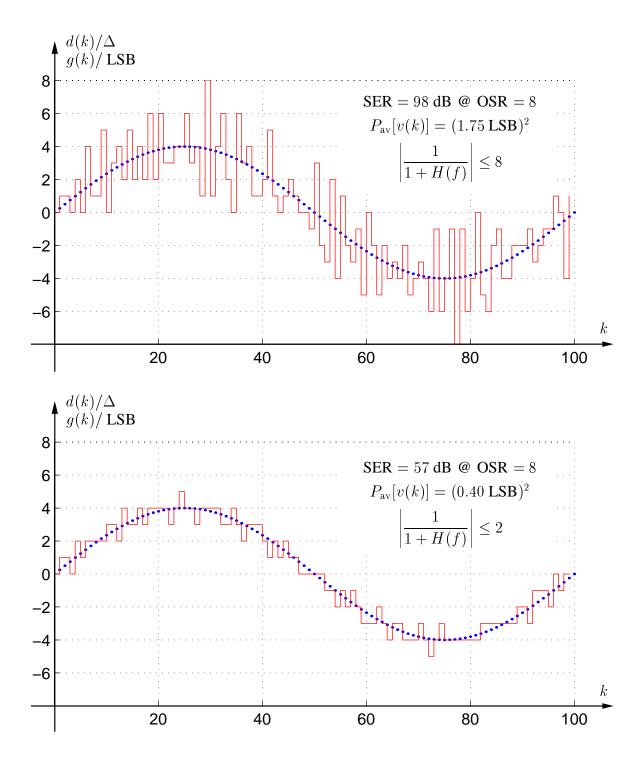

| 4.6  | Time-domain output from two multi-bit delta-sigma quantizers  |

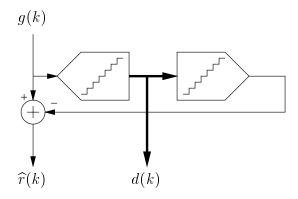

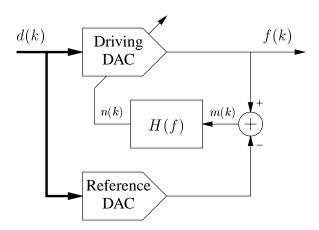

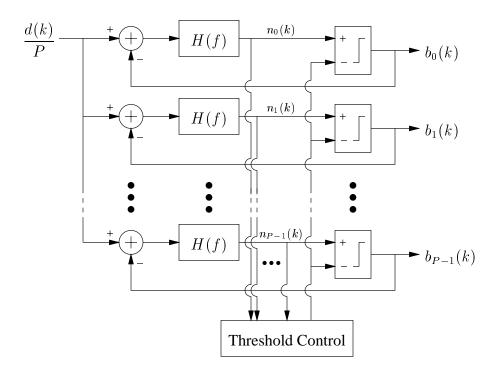

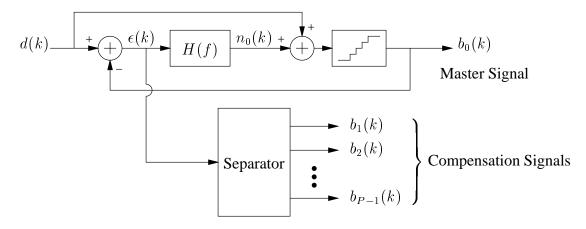

| 4.7  | Conceptual mismatch-shaping D/A converter                     |

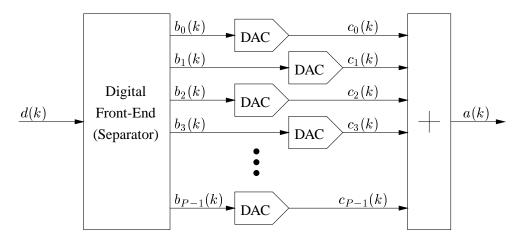

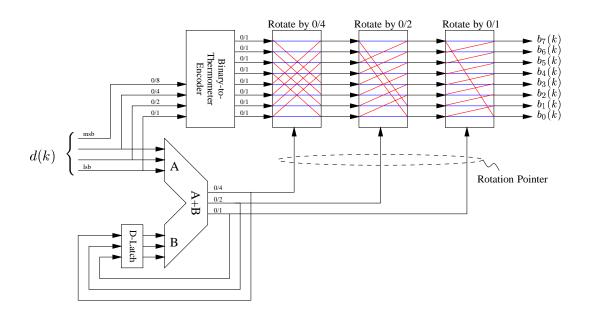

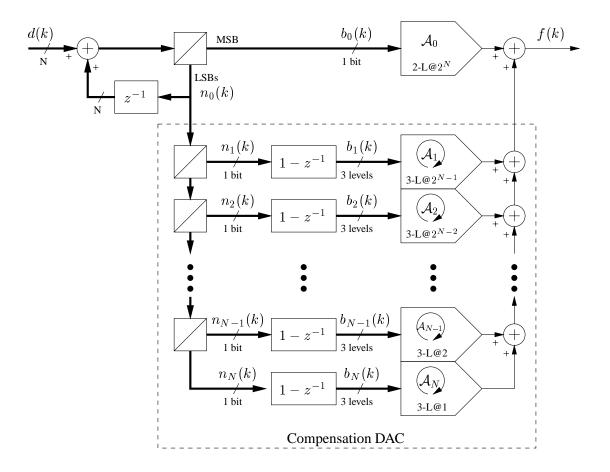

| 4.8  | Topology of most mismatch-shaping D/A converters              |

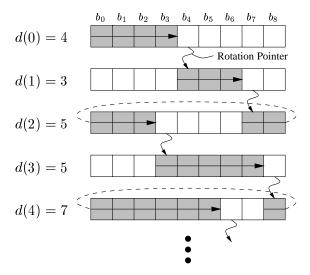

| 4.9  | Element-rotation scheme                                       |

| 4.10 | Implementation of the element-rotation scheme                 |

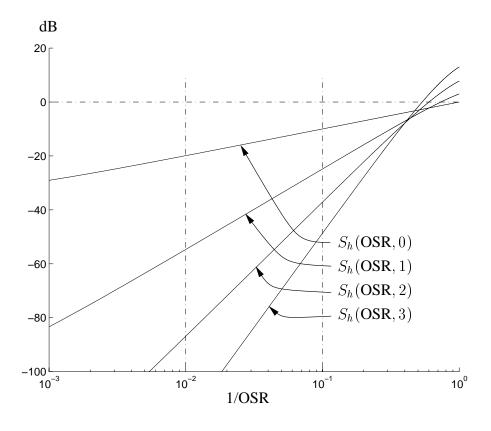

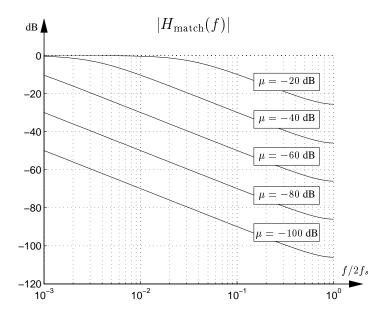

| 4.11 | Signal-band power of differentiated white-noise errors        |

| 4.12 | Symbol for UE-MS D/A converters                               |

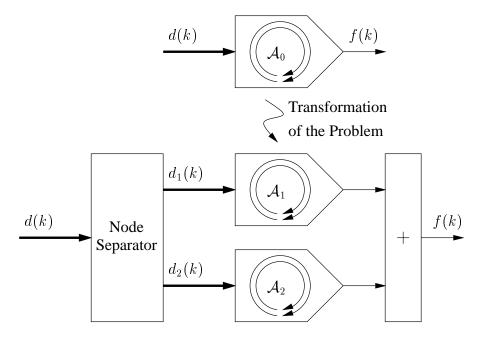

| 4.13 | Transformation used for tree-structure UE-MS D/A converters   |

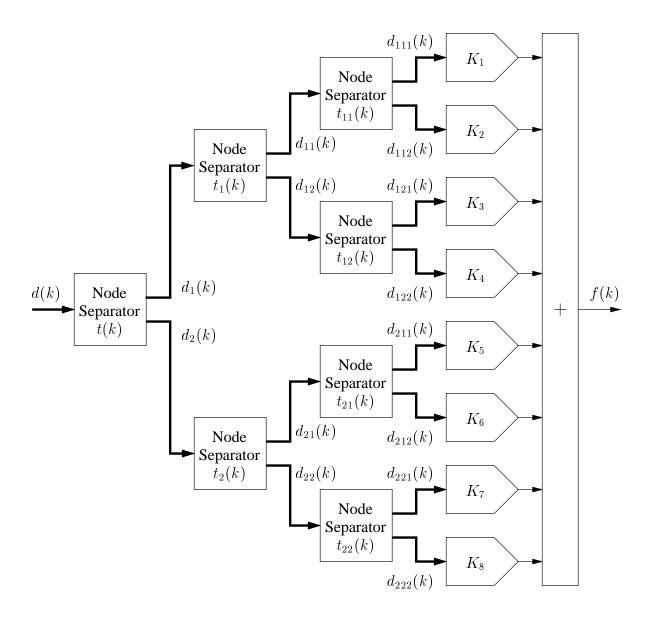

| 4.14 | Tree-structured UE-MS D/A converter                           |

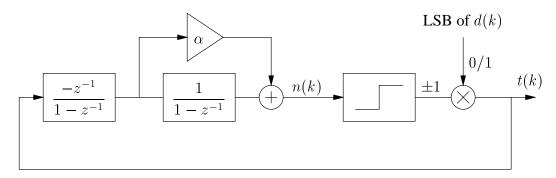

| 4.15 | Node separator used in tree-structure UE-MS D/A converters    |

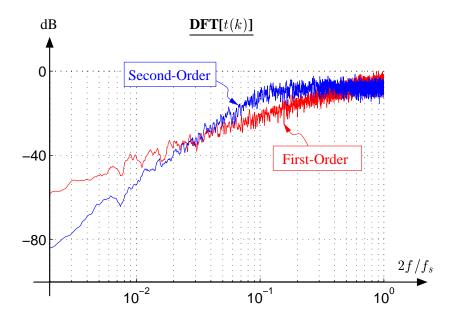

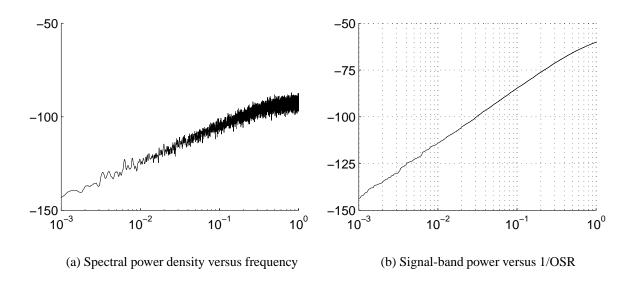

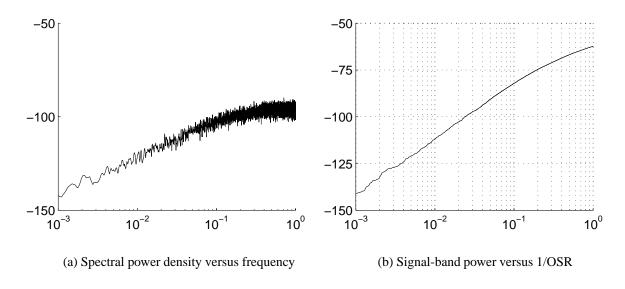

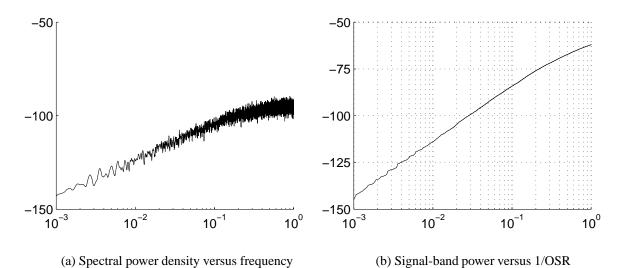

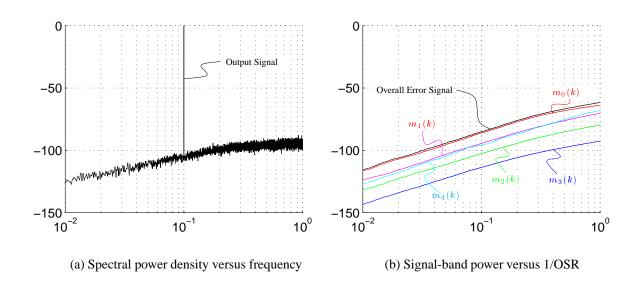

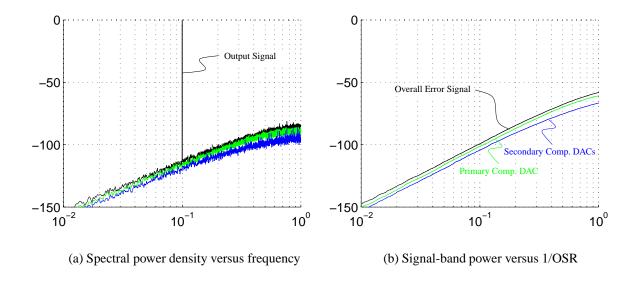

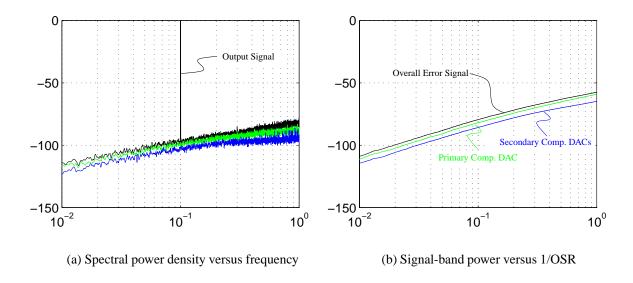

| 4.16 | Spectral power density of UE-MS D/A converters' error signals |

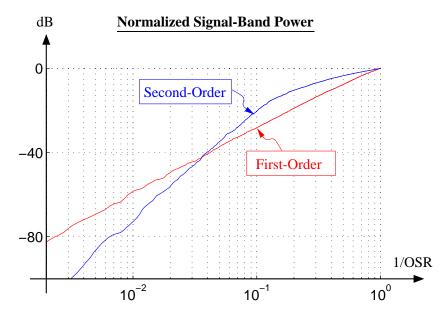

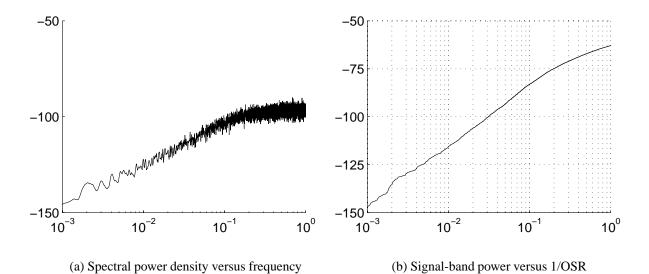

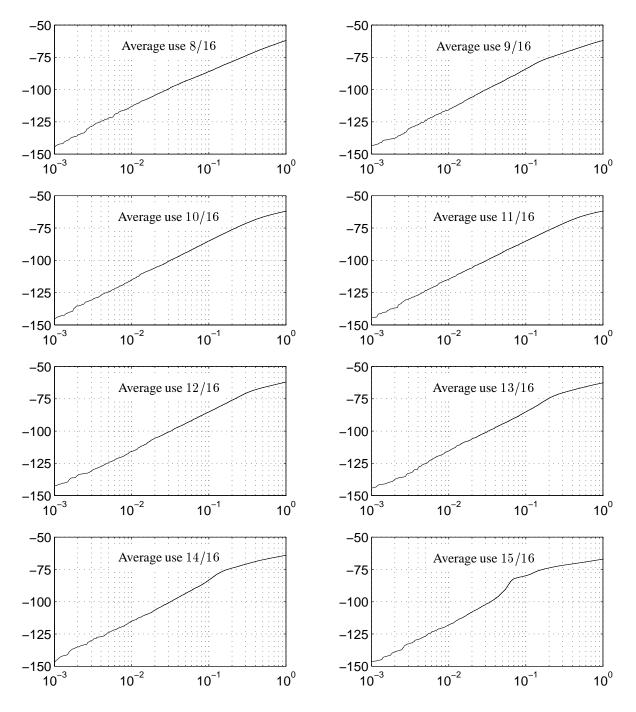

| 4.17 | Signal-band power of UE-MS D/A converters' error signals      |

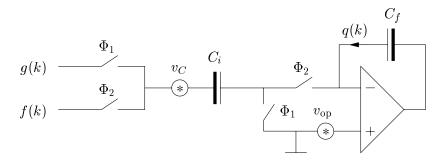

| 4.18 | Input stage of a switched-capacitor delta-sigma quantizer     |

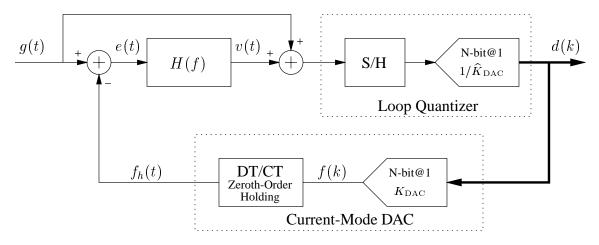

| 4.19 | Continuous-time delta-sigma quantizer                         |

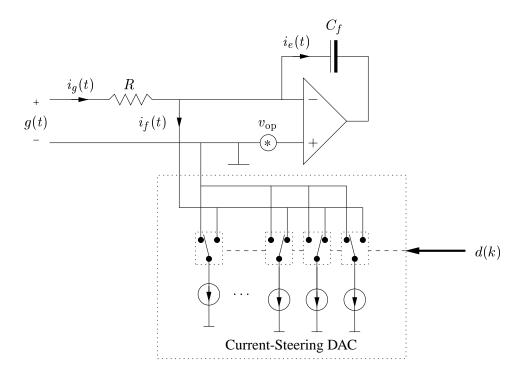

| 4.20 | Input stage of a continuous-time delta-sigma quantizer        |

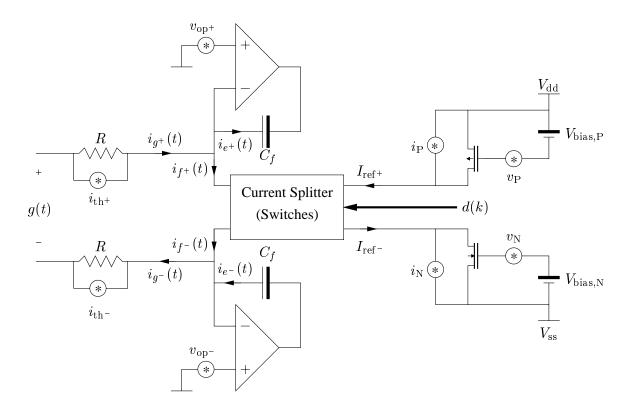

| 4.21 | Noise model of a continuous-time delta-sigma quantizer        |

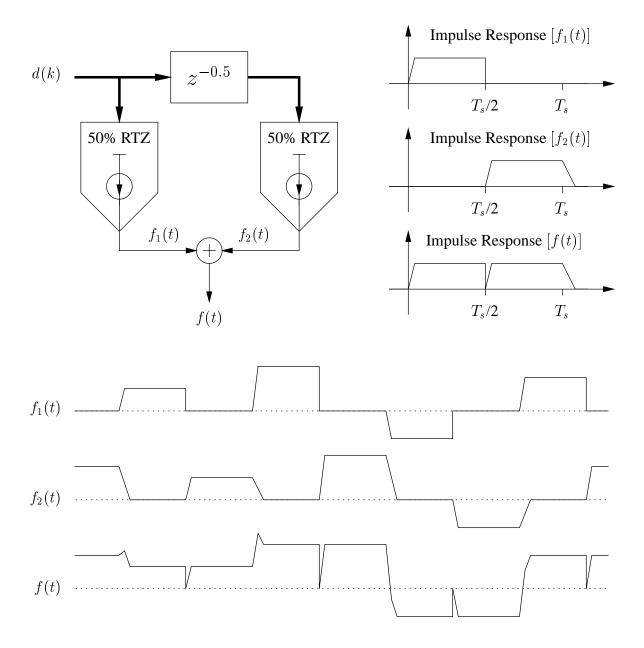

| 5.1  | Dual-return-to-zero current-mode D/A converter                |

xvi LIST OF FIGURES

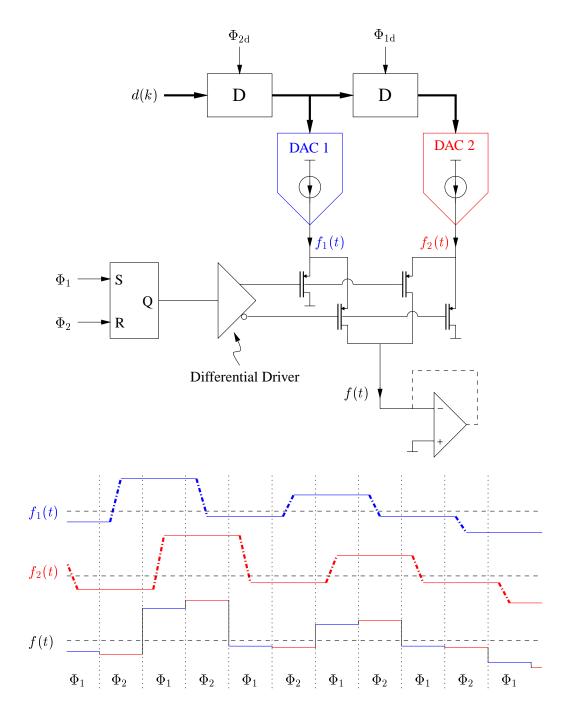

| 5.2  | Time-interleaved current-mode D/A converter                                       |

|------|-----------------------------------------------------------------------------------|

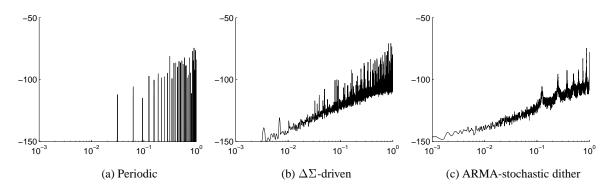

| 6.1  | Idle tones in element-rotation-scheme UE-MS D/A converters                        |

| 6.2  | Idle tones in tree-structure UE-MS D/A converters                                 |

| 6.3  | Spectral performance of tree-structure UE-MS D/A converter (small input)          |

| 6.4  | Spectral performance of tree-structure UE-MS D/A converter (small input)          |

| 6.5  | Static performance of tree-structure UE-MS D/A converters                         |

| 6.6  | Dithering principle for element-rotation-scheme UE-MS D/A converters              |

| 6.7  | Spectral performance of dithered ERS UE-MS D/A converter (small input) 155        |

| 6.8  | Spectral performance of dithered ERS UE-MS D/A converter (large input)            |

| 6.9  | Static performance of dithered ERS UE-MS D/A converters                           |

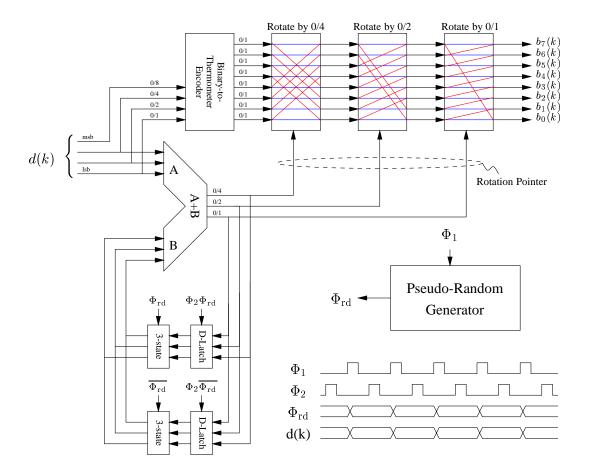

| 6.10 | Implementation of dithered ERS UE-MS encoder                                      |

| 6.11 | Equilibrium states in generalized rotation-scheme UE-MS encoders                  |

| 6.12 | Dithered randomized-rotation UE-MS encoder                                        |

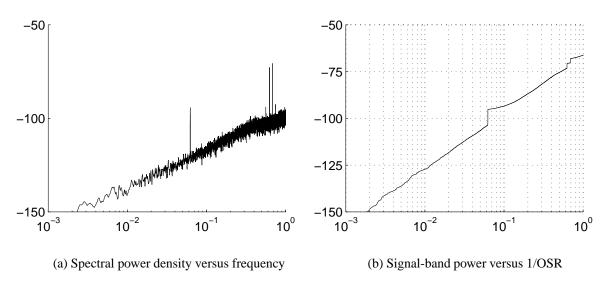

| 6.13 | Spectral performance of randomized-rotation UE-MS D/A converter (small input) 162 |

| 6.14 | Spectral performance of randomized-rotation UE-MS D/A converter (large input) 162 |

| 6.15 | Static performance of randomized-rotation UE-MS D/A converters                    |

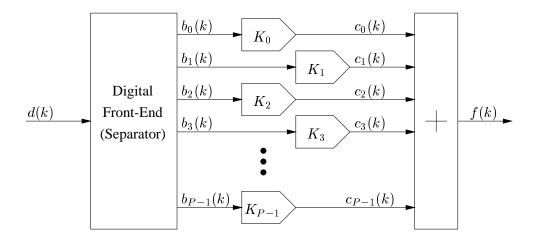

| 7.1  | Parallel UE-MS encoder                                                            |

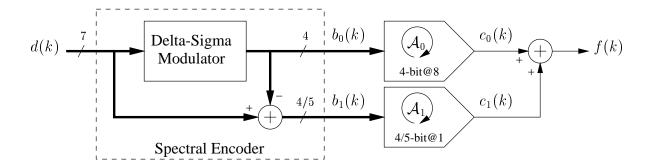

| 7.2  | Spectral encoder for SE-MS D/A converters                                         |

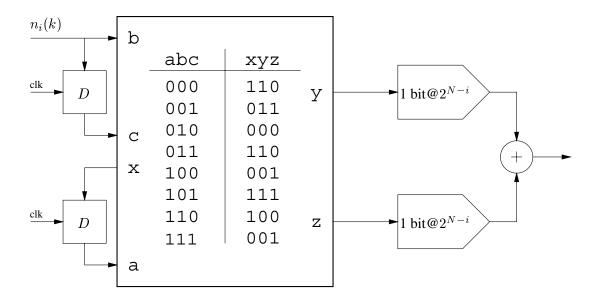

| 7.3  | Building block for SE-MS D/A converters                                           |

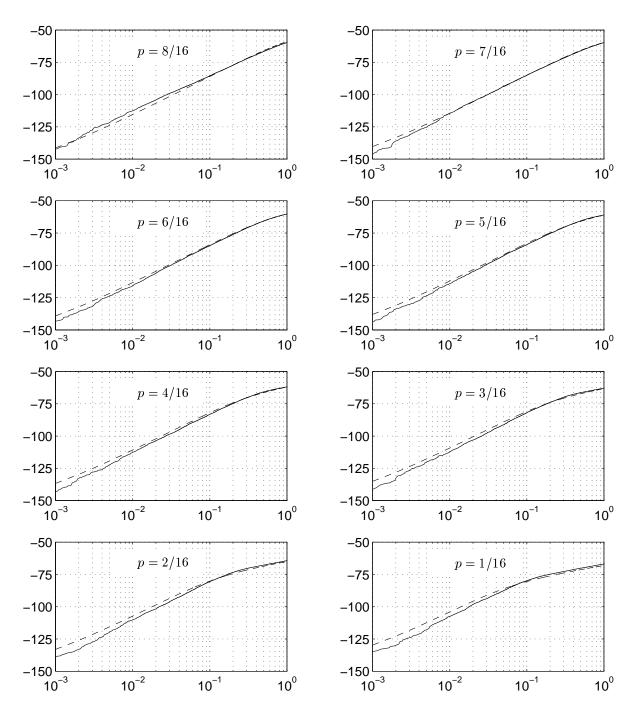

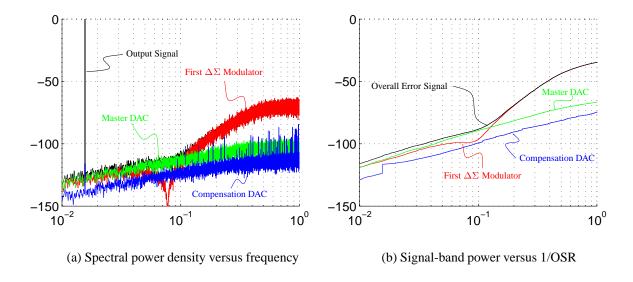

| 7.4  | Simulated performance of first-order SE-MS D/A converters                         |

LIST OF FIGURES xvii

| 7.5  | Symmetrical-tree SE-MS D/A converter                                                |

|------|-------------------------------------------------------------------------------------|

| 7.6  | Asymmetrical-tree SE-MS D/A converter                                               |

| 7.7  | Implementation of symmetrical-tree first-order spectral encoder                     |

| 7.8  | One-sided tree-structure SE-MS D/A converter                                        |

| 7.9  | Simulated performance of one-sided tree-structure SE-MS D/A converter               |

| 7.10 | Minimalist filtering first-order SE-MS D/A converter                                |

| 7.11 | 3-level UE-MS D/A converter for use in filtering SE-MS D/A converters               |

| 7.12 | Improved filtering first-order SE-MS D/A converter                                  |

| 7.13 | More improved filtering first-order SE-MS D/A converter                             |

| 7.14 | Optimized filtering first-order SE-MS D/A converter                                 |

| 7.15 | Generalized filtering second-order SE-MS D/A converter                              |

| 7.16 | Minimalist generalized filtering SE-MS D/A converter                                |

| 7.17 | Switched-capacitor implementation of second-order SE-MS D/A converter               |

| 7.18 | Simulated performance of generalized filtering second-order SE-MS D/A converter 197 |

| 7.19 | Simulated performance of filtering first-order SE-MS D/A converter                  |

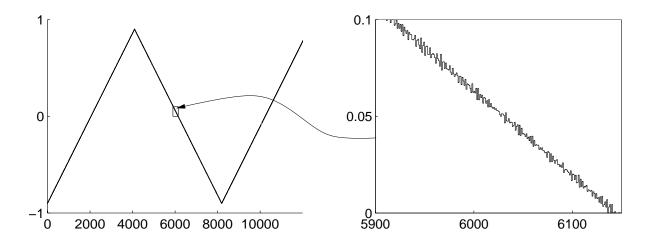

| 7.20 | Output waveform from a high-resolution SE-MS D/A converter                          |

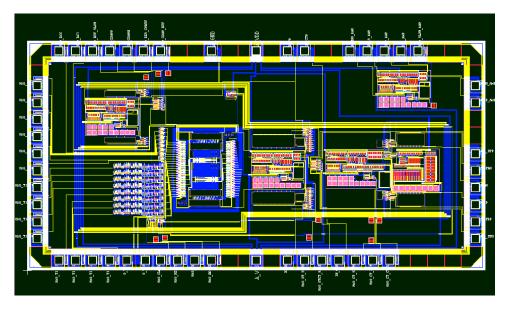

| 7.21 | Layout of test chip                                                                 |

| 7.22 | Three-level switched-capacitor D/A converter                                        |

| 7.23 | Linear three-level switched-capacitor D/A converter                                 |

| 7.24 | Linear three-level single-ended switched-capacitor D/A converter                    |

| 7.25 | Linear three-level current-mode D/A converter                                       |

xviii LIST OF FIGURES

| 7.26 | Current-mode second-order SE-MS D/A converter                                          |

|------|----------------------------------------------------------------------------------------|

| 7.27 | Filtering current-mode D/A converter                                                   |

| 7.28 | Improved filtering current-mode D/A converter                                          |

| 8.1  | Traditional single-stage multi-bit delta-sigma quantizer                               |

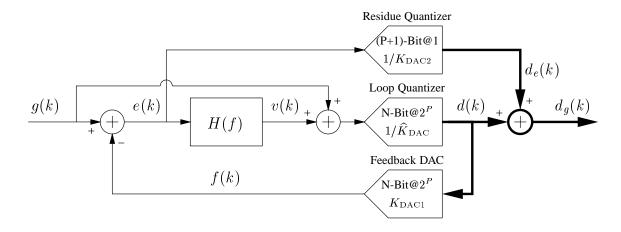

| 8.2  | Delta-sigma quantizer with digital-domain feed-forward path                            |

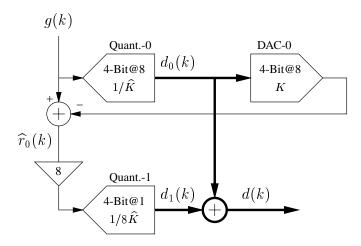

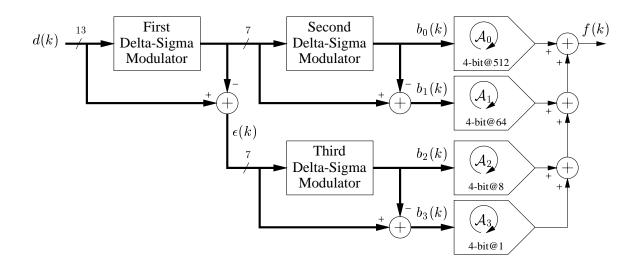

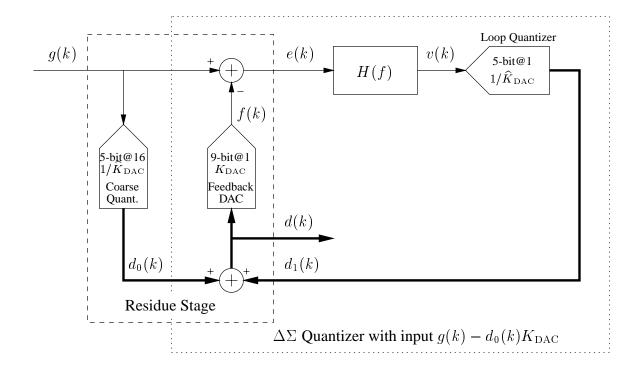

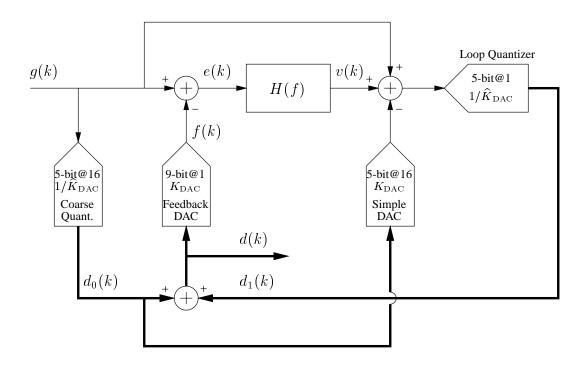

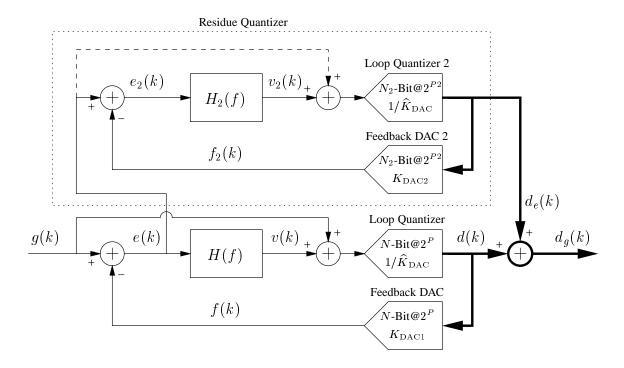

| 8.3  | Nonoptimized two-stage delta-sigma quantizer                                           |

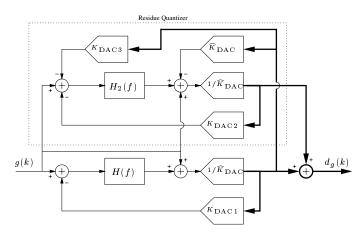

| 8.4  | Optimized two-stage delta-sigma quantizer                                              |

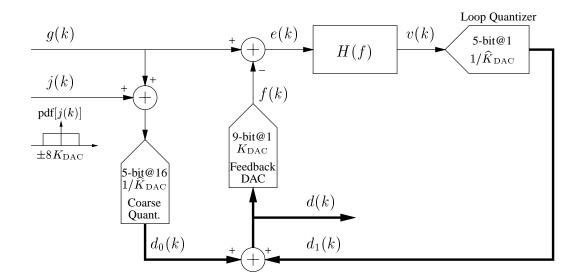

| 8.5  | Dithered nonoptimized two-stage delta-sigma quantizer                                  |

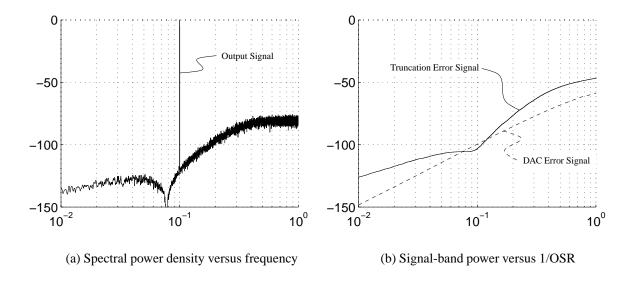

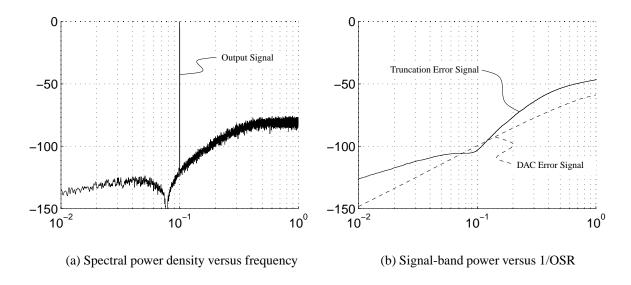

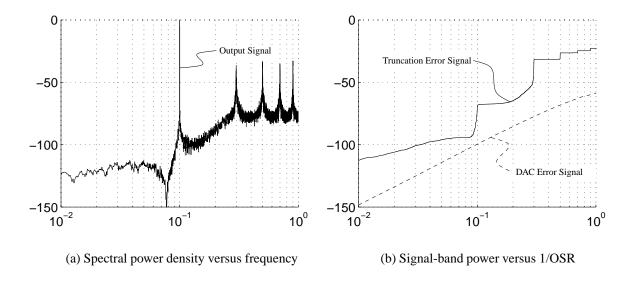

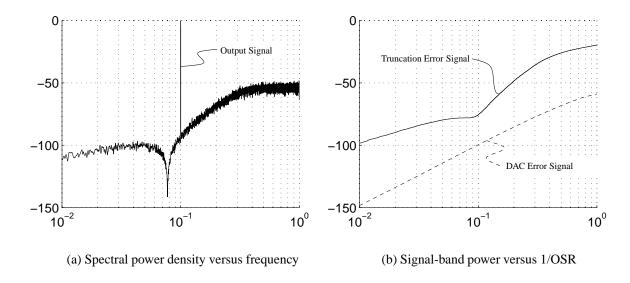

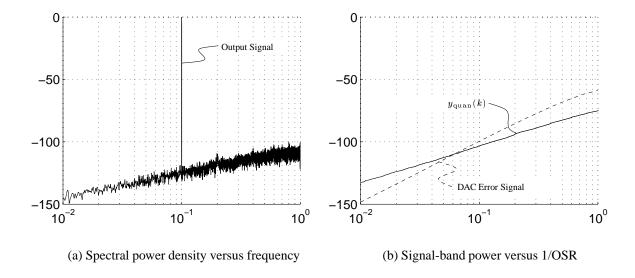

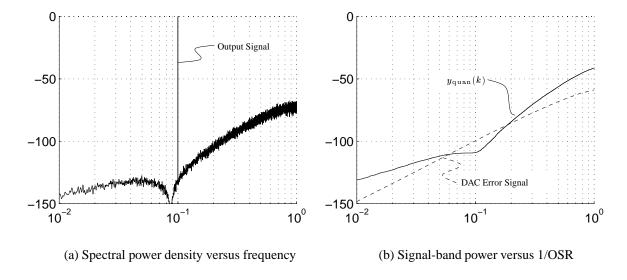

| 8.6  | Simulated performance of the single-stage delta-sigma quantizer                        |

| 8.7  | Simulated performance of the optimized two-stage delta-sigma quantizer                 |

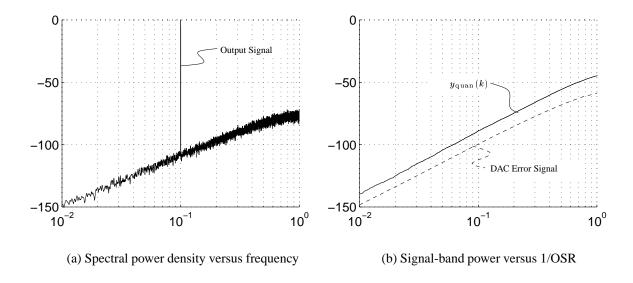

| 8.8  | Simulated performance of the nonoptimized two-stage delta-sigma quantizer              |

| 8.9  | Simulated performance of the dithered nonoptimized two-stage delta-sigma quantizer 220 |

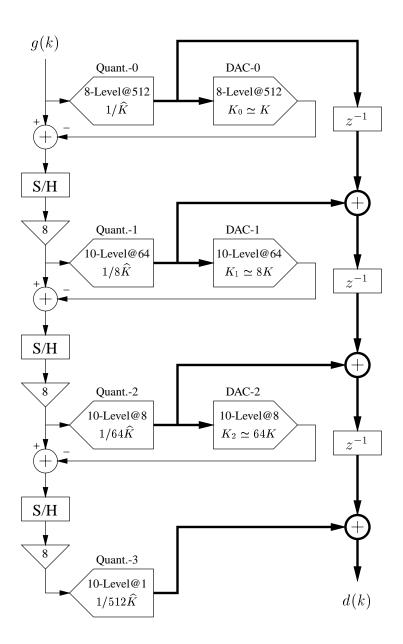

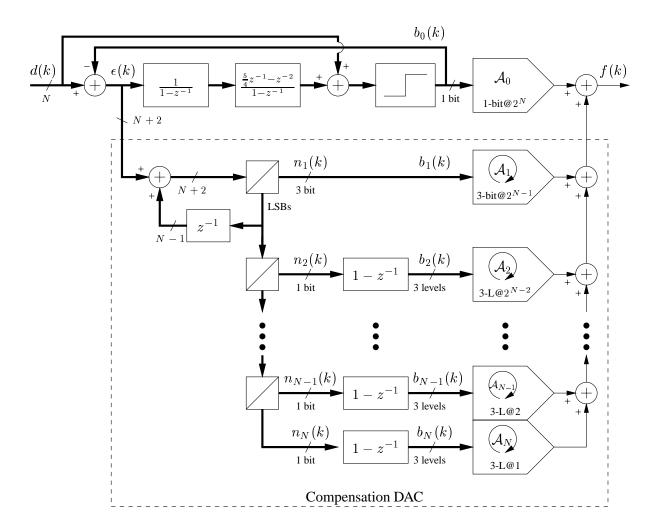

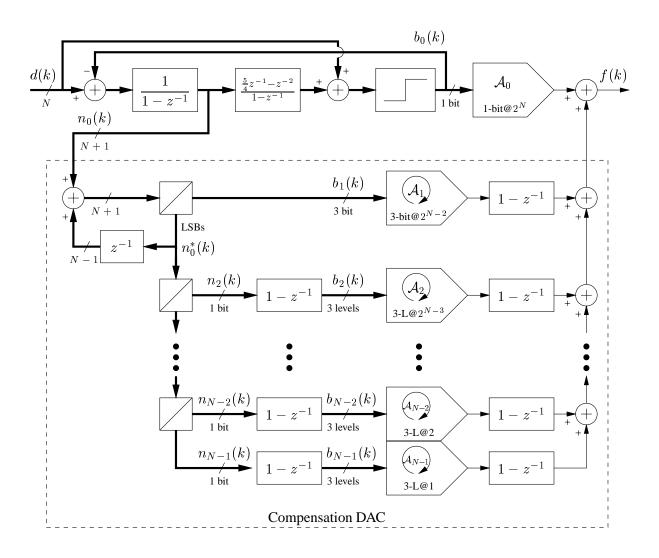

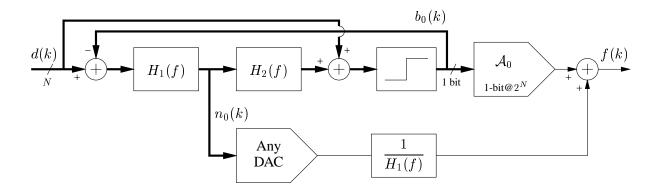

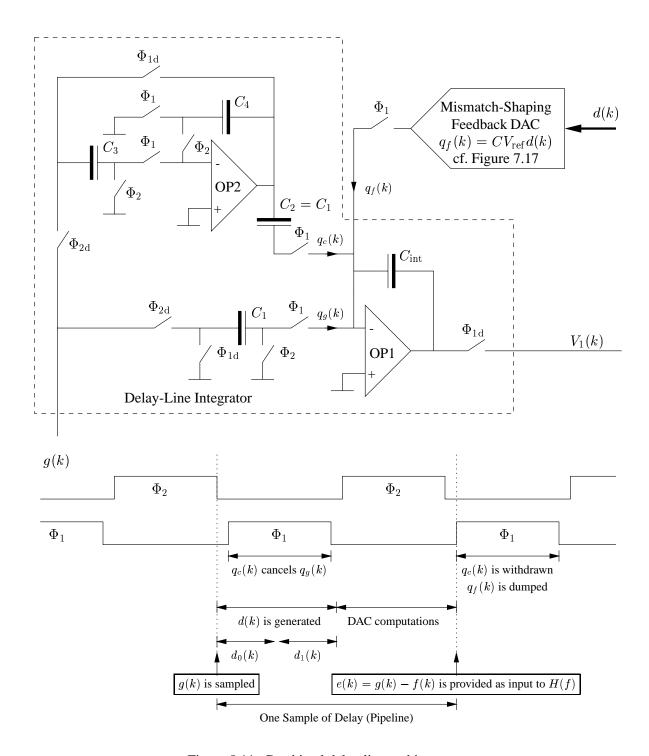

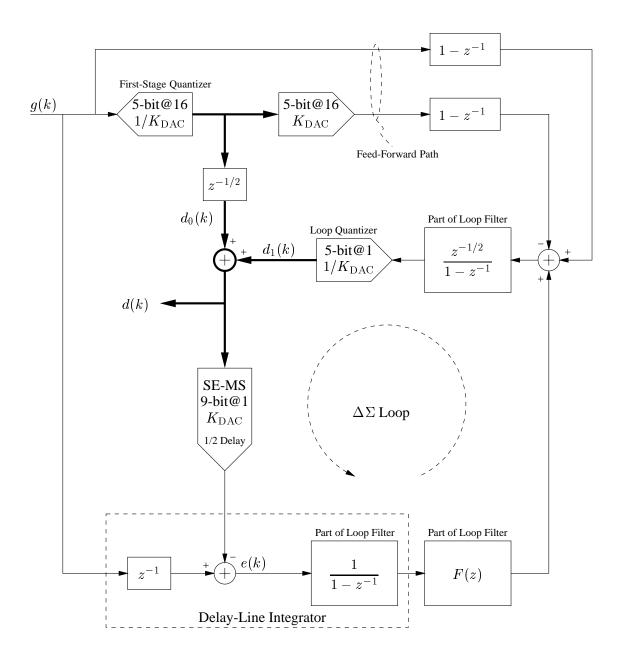

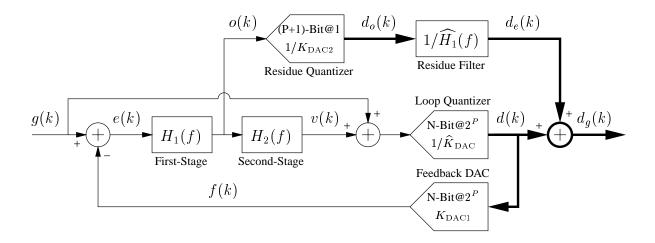

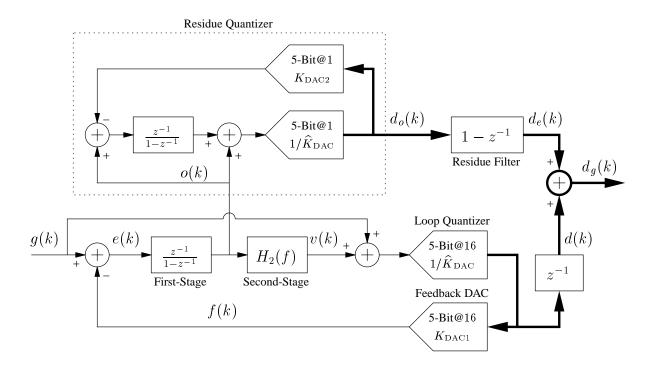

| 8.10 | Pipeline two-stage delta-sigma quantizer                                               |

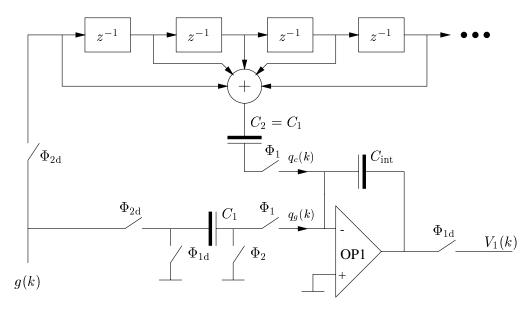

| 8.11 | Implementation of a switched-capacitor delay-line integrator                           |

| 8.12 | Generalized delay-line integrator                                                      |

| 8.13 | Pipeline two-stage delta-sigma quantizer (system-level)                                |

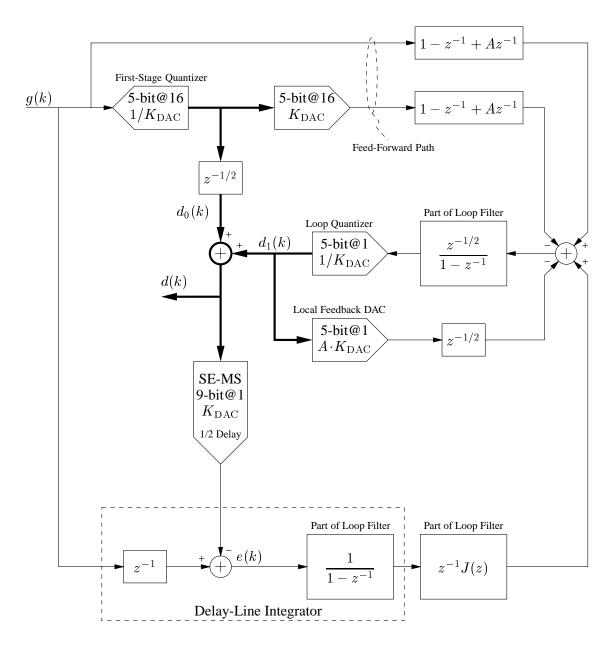

| 8.14 | Improved pipeline two-stage delta-sigma quantizer (system-level)                       |

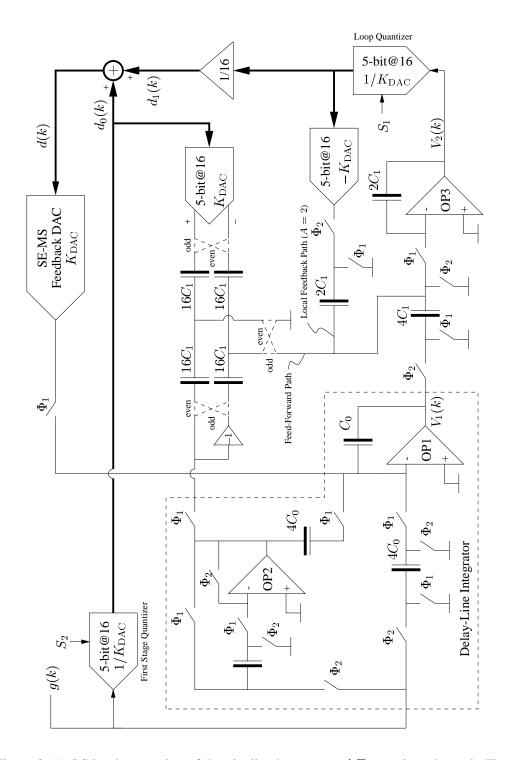

| 8.15 | Improved pipeline two-stage delta-sigma quantizer (circuit-level)                      |

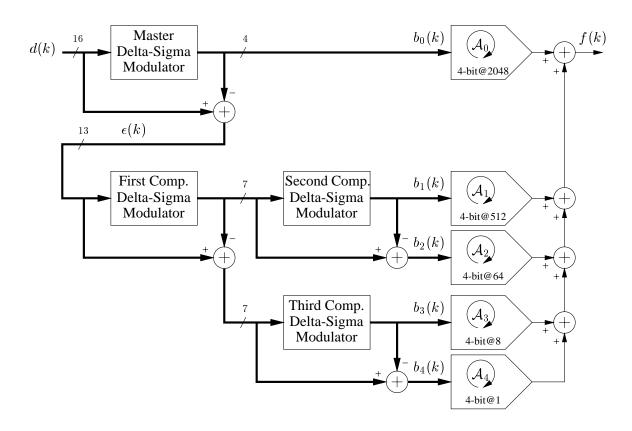

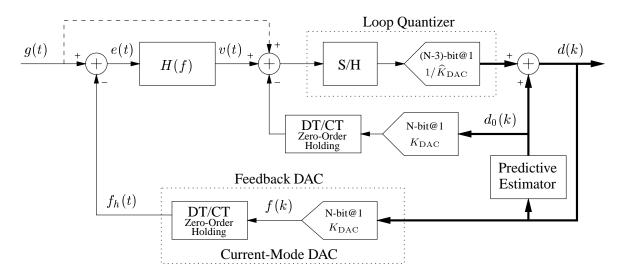

| 9.1  | Directly residue-compensated delta-sigma quantizer                                     |

| 9.2  | Dual-loop directly residue-compensated delta-sigma quantizer                           |

LIST OF FIGURES xix

| 9.3  | Indirectly residue-compensated delta-sigma quantizer                                   |

|------|----------------------------------------------------------------------------------------|

| 9.4  | Performance of residue-compensated delta-sigma quantizer (data-quantizer)              |

| 9.5  | Indirectly residue-compensated delta-sigma quantizer (signal quantizer)                |

| 9.6  | Performance of residue-compensated delta-sigma quantizer (signal-quantizer) 242        |

| 9.7  | Performance of residue-compensated delta-sigma quantizer (better signal-quantizer) 243 |

| 9.8  | Suppression of the truncation error obtained by compensation                           |

| 9.9  | Predictive delta-sigma quantizer (continuous-time loop filter)                         |

| 9.10 | Delay-compensated continuous-time residue-compensated $\Delta\Sigma$ quantizer         |

XX LIST OF FIGURES

## **List of Tables**

| 4.1 | Oversampling ratio required for single-bit delta-sigma quantizers | 85  |

|-----|-------------------------------------------------------------------|-----|

| 4.2 | Oversampling ratio required for multi-bit delta-sigma quantizers  | 95  |

| 9.1 | Opamp gain needed for residue-compensated delta-sigma quantizers  | 247 |

xxii LIST OF TABLES

### Chapter 1

### Introduction

Modern society relies on signal processing. It is applied in communication equipment, medical devices, automated production facilities, computers, weapons, navigation equipment, tools and toys, etc.. Most human-designed signal processing is performed by electronic circuits, and the range of applications is broadened as these circuits are perfected and their costs reduced.

The majority of the signals of interest are found in the world that surrounds us, whether it relates to monitoring a heart or guiding a missile. The first step performed by a signal-processing system is to convert a considered signal into a form that can be processed by an electronic circuit. Sometimes a dedicated electro-mechanical system (called a *sensor*) will be required to sense the signal and convert it into a voltage, charge, or current signal, and sometimes the signal is readily available in one of these forms. An electronic circuit will then process the electric signal in a specified way, and the outcome will often be applied to a nonelectronic task, such as displaying an image of the heart, or adjusting the missile's direction of flight.

The signal processing that needs to be performed can vary from very simple operations (e.g., amplification) to extremely complex ones involving computation of several parameters, such as standard deviation, spectral composition, correlation coefficients, etc.. A fundamental property of analog electric signal processing is that each operation will be associated with a degradation of the signal-to-noise ratio (SNR).

Hence, if substantial analog signal processing (ASP) is performed, stochastic artifacts (noise) will accumulate, and the resulting signal may not represent the desired signal with the required significance. Furthermore, the accuracy of ASP is inherently limited; the linearity of supposedly linear operations is not ideal, multiplication of signals is poorly implemented, etc..

A wide range of applications require substantial amounts of highly accurate signal processing. High-accuracy electronic signal processing can generally be implemented only when the signals are represented in digital form. In digital form, signals can be processed with arbitrary resolution and accuracy and without noticeably degrading the SNR. However, many thousands of transistors are required to implement a circuit that performs only simple digital signal processing (DSP). Hence, the feasibility of DSP is mainly a matter of circuit density and power consumption.

Thanks to CMOS integrated circuit technology, DSP has experienced explosive growth during the last couple of decades. CMOS technology has become widely available and it is characterized by an outstanding cost-to-performance ratio which is improved steadily (Moore's Law). CMOS technology's many advantages include its low cost, high speed, high circuit density, low power consumption per operation, and the availability of software for the semi-automated design of DSP circuits. The cost and efficiency of CMOS-based DSP is actually so competitive that it is often used for the implementation of even simple signal processing systems where ASP could potentially be used instead. The fields that remain dominated by ASP include high-frequency (radio) signal processing and applications that are characterized by low resolution and a high degree of parallelism (for example, finger-print sensors).

Data converters are the missing link needed for the implementation of a DSP-based electronic circuit. Although digital signals can be processed with arbitrary resolution and accuracy, the system's overall performance cannot exceed the resolution or accuracy by which the considered analog signals can be converted into digital form (A/D conversion), or by which the processed digital signal can be reconverted into analog form (D/A conversion). Obviously, data conversion is not a new discipline in circuit design, but huge industrial investments are still being made, and there is a tremendous research activity continuing in this technical field. This clearly shows that there is a great demand for CMOS-based data converters that combine high speed, high resolution, and low cost.

<sup>&</sup>lt;sup>1</sup>Several hundred million transistors can be employed in the same circuit.

3

#### 1.1 The Class of Data Converters Considered

This work focuses almost exclusively on delta-sigma modulation as the chosen technique for A/D and D/A conversion. Delta-sigma ( $\Delta\Sigma$ ) converters have gained popularity during the last decade because they trade an increased requirement for DSP for a relaxed requirement for high-performance analog circuit blocks. Single-bit  $\Delta\Sigma$  converters have usually been preferred because they avoid the requirement for accurately matched electrical parameters that characterize most other high-resolution data converters.

**Delta-Sigma Modulation.** Any signal is uniquely characterized by its spectral composition. This work is dedicated to the large range of applications that characterize signals by their spectral composition in only a selected frequency band (the signal band). Nyquist's sampling theorem states that the maximum bandwidth that can be represented by a uniformly-sampled digital signal is half the signal's sampling frequency (the Nyquist bandwidth), in which case there is a one-to-one correspondence between the signal's spectral composition and the value of its samples. However, if the signal is oversampled, i.e., if it is characterized by its spectral composition in a signal band which is narrower than the Nyquist bandwidth, then the value of each sample is not uniquely defined, and the flexibility can be used (for example) to truncate the signal's samples to values from a finite set of selected values. More precisely, there is a tradeoff between the signal's oversampling ratio (OSR) and the tolerance allowed in each sample's value. The samples' truncation errors must be correlated to preserve the signal-band spectral composition, and the process somewhat resembles interpolation. The tradeoff between resolution and bandwidth is considered good. For example, the same signal can be represented by truncation to 65,536 uniformly-spaced values using only negligible oversampling, or by truncation to only 2 values using 32 times oversampling<sup>4</sup>.

<sup>&</sup>lt;sup>2</sup>Two signals are considered to be equivalent if their spectral composition in the signal band is identical (or if the difference is smaller than a chosen threshold, say -100 dB full scale). The flexibility reflects that spectral variations outside the signal band are allowed.

<sup>&</sup>lt;sup>3</sup>The Nyquist bandwidth divided by the signal's bandwidth.

<sup>&</sup>lt;sup>4</sup>The minimum required oversampling ratio expressed as a function of the signal and the selected set of truncation levels is not known, but would probably be of little practical interest. The numbers provided herein characterize circuits that can perform the discussed translation from one representation to another.

In essence,  $\Delta\Sigma$  modulators are circuits that can translate a signal between representations of different resolutions and sampling rates.

Single-Bit Delta-Sigma Converters. Single-bit (two-level) signal representation is useful because it facilitates linear A/D and D/A conversion without relying on accurate matching of electrical parameters [1]. This is why the technique has become popular. Although signals can be  $\Delta\Sigma$  modulated into a two-level representation using only 32 times oversampling, there are several practical reasons why this is rarely done. Usually, oversampling ratios in the order of 128 are used, which, unfortunately, considerably constrains the system's bandwidth because the maximum sampling frequency cannot be increased arbitrarily. Single-bit  $\Delta\Sigma$  converters have, therefore, been used mainly for audio and other high-performance applications which have a fairly low bandwidth.

Multi-Bit Delta-Sigma Converters. A  $\Delta\Sigma$  data converter's linearity is constrained by the linearity of a D/A converter employed internally. The inherent linearity of time-invariant single-bit D/A converters (DACs) is the key to single-bit  $\Delta\Sigma$  converters' superb linearity.

Multi-bit  $\Delta\Sigma$  converters can operate at a substantially lower OSR than their single-bit counterparts, even if the signal is represented by only a few bits of resolution [2]. They are, therefore, more suitable for wide-bandwidth data conversion, which is required by a wide range of applications. Unfortunately, a DAC's full-scale linearity is essentially independent of its resolution (except for single-bit DACs), hence  $\Delta\Sigma$  modulation does not directly offer any advantages for non-single-bit data converters. However, it is indeed simpler to calibrate a low-resolution DAC than it is to calibrate a high-resolution one, and multi-bit  $\Delta\Sigma$  modulation has successfully been used for calibrated systems [1,3,4].

The introduction of mismatch-shaping DACs marked a major breakthrough in multi-bit  $\Delta\Sigma$  data conversion. The fundamental principle employed by these DACs is that they are allowed to produce inaccurate analog output values, as long as they interpolate between the errors and the output signal's signal-band spectral composition remains intact. This operation is very similar to  $\Delta\Sigma$  modulation.

The basic requirement for mismatch-shaping DACs is that they must be able to interpolate between the mismatch errors without knowing the actual value of each error. This operation can, for example, be ob-

5

tained when using a digital state machine to control a unit-element DAC<sup>5</sup> [1,2,5–18]. The complexity of unit-element mismatch-shaping DACs increases considerably with their resolution, hence the technique is suitable only for DACs with a resolution of up to (say) 6 bits. In other words, a  $\Delta\Sigma$  modulator is required to reduce the signal's resolution to a level where a mismatch-shaping DAC can be implemented using only circuitry of reasonable complexity.

High-Resolution Mismatch-Shaping Data Converters. Through the development of digital state machines that can implement scaled-element DACs<sup>6</sup> with mismatch shaping, this work extends the possibilities for high-resolution data conversion. The circuit complexity of the proposed state machines is low, and the mismatch-shaping DACs' resolution can be made arbitrarily high. Because the signal is not interpolated to a low-resolution representation, large spectral components outside the signal band (representing the truncation error) will not occur, and the specifications of the filters that are normally required to remove such spectral components can, therefore, be relaxed considerably. Hence, the proposed techniques facilitate the implementation of high-speed D/A converters that are characterized by an unpreceded simplicity and level of performance (100 dB performance at 10 times oversampling is feasible using an inexpensive standard CMOS technology with no post-production calibration).

The proposed mismatch-shaping DACs need not cause substantial delay, hence they are well suited for use in multi-bit  $\Delta\Sigma$  A/D converters. Usually, the D/A converter employed internally in  $\Delta\Sigma$  A/D converters has been the limiting factor for the overall performance, but when a scaled-element mismatch-shaping DAC is used for this purpose, the performance can be improved to the level where it is only the complexity of the internal loop quantizer that will limit the performance. This work also proposes techniques that solve this complexity problem. Using the proposed techniques, the achievable performance reaches a level where only device noise, clock jitter, and other unavoidable effects will constrain the performance.

<sup>&</sup>lt;sup>5</sup>Unit-element DACs generate the analog output signal by adding analog sources of the same nominal value.

$<sup>^6</sup>$ Scaled-element DACs generate the analog output signal by adding analog sources of scaled nominal values. Binary-weighted DACs (for which the analog sources are proportional to  $1, 2, 4, 8, \ldots$ ) are an example which illustrates that the resolution of scaled-element DACs can be vastly higher than the resolution of unit-element DACs based on the same number of analog sources.

#### 1.2 The Structure of This Thesis

Following this Introduction, Chapter 2 begins by defining the class of signals considered and the main mathematical tool used to characterize and analyze them (the Fourier transform). Methods for estimating a signal's spectral composition are also discussed. The chapter includes only material that should be common knowledge for all trained electrical engineers, so it may be considered as optional reading.

Chapter 3 is a discussion of the basic aspects of data conversion. It discusses the basic steps and the topologies in which most A/D and D/A converters are implemented (but it is not comprehensive). It provides several definitions, and it points out some of the many effects that are likely to limit a data converter's performance. The reader is advised to be familiar with this material.

Chapter 4 is an overview of state-of-the-art  $\Delta\Sigma$  quantizers, and it includes a thorough discussion of mismatch-shaping unit-element DACs. It outlines the advantages of multi-bit  $\Delta\Sigma$  modulation, and it points out the drawbacks of the so-called MASH quantizers. It also includes an evaluation of the best-case noise performance, which ultimately will limit the overall performance. Even the reader with good insight in  $\Delta\Sigma$  data conversion is advised to read this chapter carefully.

Chapters 5, 6, 7, 8, and 9 constitute the main part of this work, and at least 90% of the material contained in them is believed to be novel.

Chapter 5 is a discussion of how dynamic errors can be avoided in current-mode DACs. Current-mode DACs are important because they facilitate the implementation of data converters with a very low noise floor (discussed in Chapter 4).

Chapter 6 is a discussion of idle tones in mismatch-shaping DACs. Idle tones are a very unpleasant (and hence important) phenomenon which has received little attention in the open literature. Several techniques to prevent idle tones are proposed.

Chapter 7 is a discussion of the design of scaled-element mismatch-shaping DACs and possibly the most important part of this thesis. Several techniques are proposed.

Chapter 8 is a discussion of what is required to make full use of the proposed scaled-element mismatchshaping DACs when they are used for the implementation of high-resolution  $\Delta\Sigma$  quantizers. Pipeline techniques are proposed as a way to avoid the need for high-resolution flash quantizers.

Chapter 9 takes a different approach for the design of high-performance  $\Delta\Sigma$  quantizers. The technique is based on a multiple-stage quantization, which somewhat resembles MASH-topology  $\Delta\Sigma$  quantizers. The major advantage of the proposed technique (as opposed to MASH quantizers) is that it does *not* rely on accurate matching of analog and digital filters, therefore, high-performance low-complexity quantizers can be implemented robustly.

#### 1.3 Intellectual Property Rights

This serves as a public notice that several U.S. and international patents are pending for substantial parts of this work. The reader is advised to contact the author (Steensgaard@ieee.org) for licensing information before employing the discussed techniques in commercial products.

### Chapter 2

## **Characterization of Signals**

This chapter will define the class of signals that are relevant for this work. The properties of analog and digital signals are discussed, and an important distinction between continuous-time and discrete-time signals is made.

Although the considered signals are defined as functions of a time index, they are often better analyzed in the frequency domain. A mathematical tool, the Fourier Transformation, is used as the fundamental link between the time domain and the frequency domain. As this technique is assumed to be common knowledge for all properly-trained electrical engineers, the main results will merely be summarized. Unfortunately, the process of estimating a signal's spectral composition on the basis of its time-domain representation in a finite-duration period of time is not always well understood. Because this work makes extensive use of such estimates, this process and its tradeoffs will be discussed in some detail.

### 2.1 Time-Domain Representation of Signals

A signal's properties can be described in many ways – too many to be discussed in this context. In this thesis, signals are assumed to be defined by their relation to the time variable.

#### 2.1.1 Analog Signals

An analog signal shall mean a physical phenomenon described by a single-variable measure, which is a continuous function of time.

A typical example of an analog signal is the electrostatic potential (voltage) at a specified location relative to a selected reference location (ground). Another typical example is current, which is defined as the first derivative of the charge passing through a specified oriented surface. Analog signals can, in principle, be measures of almost anything: angle, velocity, acceleration, temperature, energy, reflection, weight, resistance, capacitance, inductance, etc.. However, notice that because it can be described only by at least three parameters, color is not considered to be an analog signal; whereas, the light intensity at a specified wave length *is* an analog signal.

Analog signals will (as usual) be characterized by the measure, rather than by the physical phenomenon that the measure evaluates. Thus, analog signals are simply continuous mathematical functions of a variable called time. The provided circuit examples will, however, use voltage, current, and charge as examples of analog signals.

**Continuous-Time Analog Signals.** A continuous-time analog signal is an analog signal that is defined and evaluated with respect to a continuum of time values.

**Discrete-Time Analog Signals.** Although all analog signals, or at least the described physical phenomena, are defined for a continuum of time values; some analog signals are evaluated only at discrete time instances. Such analog signals are called discrete-time signals. Notice that whether an analog signal should be characterized as a continuous-time or a discrete-time signal depends only on the application to which the signal is applied, hence it is not a property that can be extracted from the signal itself.

<sup>&</sup>lt;sup>1</sup>Strictly speaking, in the classical description of charge being discretely distributed in space, current is not an analog signal according to the above definition (as current would be a sequence of impulses, and hence not a continuous function of time). However, as this thesis addresses macroscopic problems, such inconsistencies will be allowed without further notice.

Although not fully comprehensive, this thesis will only consider discrete-time signals that are uniformly-sampled. More precisely, a discrete-time analog signal  $a_d(k)$  is in this thesis defined by an analog signal's  $a_c(t), t \in R$ , values at discrete time instances, which are equidistantly spaced by a chosen constant time unit  $T_s$ . Thus, a discrete-time analog signal can be described as

$$a_d(k) = a_c(kT_s), \qquad k \in Z = \{\dots, -3, -2, -1, 0, 1, 2, 3, \dots\}$$

(2.1)

The chosen time unit  $T_s$  is called the *sampling period*, and the reciprocal of the sampling period is called the *sampling frequency*  $f_s = 1/T_s$ .

Switched-capacitor (SC) circuits are a typical example of circuits that evaluate analog signals in discrete time. SC circuits consist of one or more cells designed to settle towards a stable and well-defined equilibrium. By evaluating the signals only at time instances when the cells have settled to values very close to their equilibria, the signal processing provided by these circuits can be made accurate.

### 2.1.2 Digital Signals

This thesis will only consider a subset of the large class of signals that generally are considered to be digital signals. In the following, a digital signal shall mean a member of this subset.

Digital signals are always discrete-time signals, and their characteristics are, from a mathematical point of view, equivalent to those of discrete-time analog signals. The difference between a digital and a discrete-time-analog signal is that a digital signal is a sequence of numbers, whereas a discrete-time-analog signal is a sequence of samples/evaluations of some physical phenomenon. In other words, a digital signal d(k) is simply a sequence of numeric values that are a function of an integer variable k, which is considered to represent a sequence of equidistant time values  $t = kT_s$ .

In a physical system, a digital signal will be represented by a set of one or more analog signals (often called *bits* or *bit signals*) that, when evaluated jointly at  $t = kT_s$ , are considered to represent one of a finite number of possible states (called *codes*), each of which are considered to represent a numeric

<sup>&</sup>lt;sup>2</sup>In this way, the performance of SC circuits can be made insensitive to nonlinear settling effects etc., which can cause substantial errors in circuits operating on continuous-time signals.

value. A fundamental property of all digital systems is that each code is easily distinguishable from the other possible codes, hence the correct numeric value will be represented/detected even if the bit signals are subject to a considerable amount of noise. The *noise margin* is defined as the level of noise which can be tolerated at a given (very high) stochastic significance level of the representation of the codes. Usually, each bit signal is considered to represent one of only two possible states, high (1) or low (0), therefore the noise margin is typically very good. Using this practice, a collection of N bit signals can represent up to  $2^N$  different codes. If P evaluations of the individual bit signals are used to represent each code (serial data representation), then N bit signals can represent as many as  $2^{N+P}$  different codes. Using a sufficient number of bit signals/evaluations, digital signals with arbitrary high dynamic range can easily (and robustly) be represented in a digital system.

### 2.2 Frequency-Domain Representation of Signals

As an alternative to the time-domain representation, continuous-time as well as discrete-time signals can be described in the frequency domain. The two representations are complementary because some of a signal's properties are best described/analyzed in the time domain, whereas others are best described/analyzed in the frequency domain.

It is of particular importance that the frequency-domain representation of signals allows for the definition of the *signal-band* part of a signal, which, in essence, is the only part of the signal that is important for a given application.

The Fourier Transformation will be used as the fundamental link between the two domains. In essence, the Fourier transform of a signal represents the coefficients and angles in a uniquely-defined linear combination of sinusoids in a continuum of frequencies, this linear combination being equal to the signal.

### 2.2.1 Fourier Transformation of Continuous-Time Signals

The Fourier transform G(f) of a continuous-time signal g(t) is defined mathematically as in (2.2), where convergence is assumed.

$$G(f) = \int_{-\infty}^{\infty} g(t)e^{-j2\pi ft}dt$$

(2.2)

The inverse relation, the *Inverse Fourier Transformation*, describes that G(f) simply represents the complex coefficients to the set of signals  $e^{j2\pi ft}$ ,  $f \in R$

$$g(t) = \int_{-\infty}^{\infty} G(f)e^{j2\pi ft}df$$

(2.3)

Because  $e^{j2\pi ft}$  is an orthogonal basis<sup>3</sup>, we can define the signal's energy  $E_{ab}$  in the frequency band  $0 < f_a < f < f_b$  as

$$E_{ab}[g(t)] = 2 \int_{f_a}^{f_b} |G(f)|^2 df$$

(2.4)

Parseval's Theorem (2.5) is a special case

$$E[g(t)] = \int_{-\infty}^{\infty} g^{2}(t)dt = \int_{-\infty}^{\infty} |G(f)|^{2} df$$

(2.5)

The Fourier transformation will be denoted by  $\mathcal{F}\{\cdot\}$ , whereas the Fourier transformed signal will be denoted by capitalization of the time-domain symbol and change of the argument from t to f, i.e.  $X(f) = \mathcal{F}\{x(t)\}$ . A signal and its Fourier transform will be denoted as  $x(t) \leftrightarrow X(f)$ .

Using the Fourier Transformation. Probably the most powerful feature of the Fourier Transformation is that when a signal  $g(t) \leftrightarrow G(f)$  is applied as input to a (settled and stable) linear system with the impulse response  $h(t) \leftrightarrow H(f)$ , the output y(t) is described by

$$y(t) = g(t) * h(t) = \int_{-\infty}^{\infty} g(\lambda)h(t - \lambda)d\lambda \leftrightarrow Y(f) = G(f)H(f)$$

(2.6)

The inverse property is used less often, but it is also important

$$x(t)y(t) \leftrightarrow X(f) * Y(f) = \int_{-\infty}^{\infty} X(\lambda)Y(f-\lambda)d\lambda \tag{2.7}$$

<sup>&</sup>lt;sup>3</sup>With respect to the scalar product calculating the average value of the product of two functions.

### 2.2.2 Fourier Transformation of Discrete-Time Signals

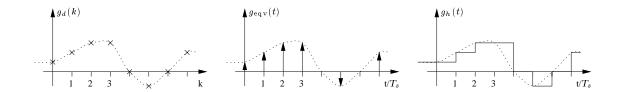

In reality, it is the same definition of the Fourier Transformation, Equation (2.2), which is applied to continuous-time as well as discrete-time signals. For this to make sense, it is necessary to define a continuous-time equivalent  $g_{\text{eqv}}(t)$  of the discrete-time signal  $g_d(k)$ , for which the Fourier transformed can be calculated using the definition.

More precisely, the Fourier transform  $\mathcal{F}_d\{\cdot\}$  of a discrete-time signal  $g_d(k)$ , sampled with the sampling period  $T_s$ , is defined as

$$G_d(f) = \mathcal{F}_d\{g_d(k)\} = \mathcal{F}\{g_{\text{eqv}}(t)\}$$

(2.8)

The discrete-time to continuous-time (DT/CT) transformation to be applied in (2.8) is defined as

$$g_{\text{eqv}}(t) = T_s \sum_{k \in \mathbb{Z}} g_d(k) \delta(t - kT_s)$$

(2.9)

The equivalent continuous-time signal  $g_{\text{eqv}}(t)$  is thus a sequence of impulses scaled according to  $g_l(k)$ , and occurring at the respective sampling instances.

Notice that  $g_{\text{eqv}}(t)$  is a mathematical abstraction, which does not represent a real-world analog signal. The DT/CT conversion (2.9) is illustrated in Figure 2.1, which also shows the DT/CT conversion (3.21) that, in general, is approximated in real-world implementations (discussed later).

Calculating the Fourier Transformed. An advantage of the above definition of the Fourier Transformation of discrete-time signals is that it is simple to calculate the Fourier transform  $G_d(f)$  of the sequence  $g_d(k)$  that is sampled from a continuous-time signal g(t), for which the Fourier transform G(f) is known. The simple relation is

$$G_d(f) = \sum_{n \in \mathbb{Z}} G(f - nf_s) \tag{2.10}$$

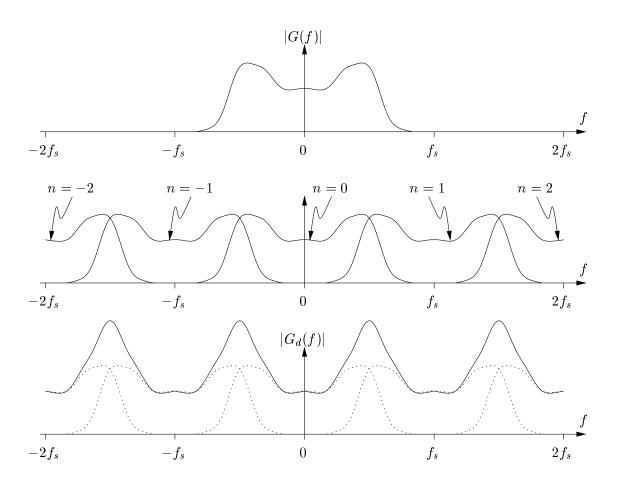

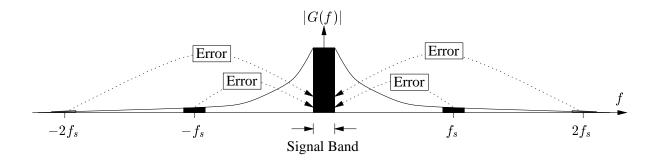

The relation (2.10) is shown graphically in Figure 2.2. At the top is shown the magnitude of the assumed Fourier spectrum |G(f)| of the continuous-time signal g(t). In the center are shown a few (for  $n \in \{-2, -1, 0, 1, 2\}$ ) of the infinitely many spectra summed in Equation (2.10). At the bottom is shown the magnitude of the sum  $|G_d(f)|$ .

Figure 2.1: Two DT/CT conversions that are commonly used for signal analysis.

Figure 2.2: A graphic interpretation of equation 2.10 illustrating aliasing.

According to Parseval's Theorem (2.5), the energy of  $g_{\text{eqv}}(t)$  is infinite, which is in agreement with the signal including impulses.

Because the Fourier Transformation for discrete-time signals is based on the Fourier Transformation for continuous-time signals, Equations (2.6) and (2.7) have trivial generalizations for discrete-time signals.

### 2.2.3 Definition of the Signal Band

The Fourier Transformation is, in principle, just a mathematical technique to separate a signal into trigonometric functions, but it should be understood that its scope reaches far beyond the mathematical level.

Several applications evaluate an applied signal by its spectral composition, rather than by its waveform or derivatives at a given time (i.e., by its time-domain representation). For example, the human ear is a highly-sophisticated electro-mechanical spectrum analyzer [19] [20], which is able to detect the spectral composition of an air-pressure signal (sound) in the frequency range from about 20 Hz to 20 kHz. Although most sensors are much less delicate than the human ear, it is invariably the case that many applications are indifferent to even very significant variations in the applied signal's spectral composition outside a certain frequency range. The frequency range in which the signal is evaluated is called the application's *signal band*.

Notice that the signal band is defined with respect to the application to which the signal is applied, and hence it is not a property that can be extracted from the signal itself. The signal band can be very different from application to application. Seismological detectors are, for example, often designed with a signal band from 0 Hz to (say) 5 Hz. Audio applications have somewhat wider signal bands (20 Hz to 20 kHz), whereas video applications and high-speed modems have signal bands which extend into the low MHz range. The signal bands of cellular phones and other wireless communication equipment are typically quite narrow frequency ranges centered around some high frequencies (the carriers, say, 900 MHz).

An application's bandwidth is considered to be the width of the signal band.

### 2.2.4 Nyquist's Sampling Theorem

Signals are sampled because it is generally easier to process them when they are represented in this format. This is true for discrete-time analog signals as well as, and in particular, for digital signals. However, there is no point in sampling a signal, unless it is possible to accurately reconstruct at least the signal-band part of the signal.

Notice that for any chosen sampling period  $T_s$  and origin of the time variable, a sampled sequence is uniquely described by the continuous-time signal from which it is generated, but that the sampling of two different continuous-time signals may result in the same discrete-time signal. In other words, the process of sampling a continuous-time signal may represent a loss of information, and the continuous-time signal can in general be reconstructed from its sampled sequence only if certain conditions are met. Nyquist's Sampling Criteria is an example of such conditions.

Reconstructing a continuous-time signal from a discrete-time signal will involve some kind of DT/CT conversion. Without loss of generality, only DT/CT conversions, which can be modeled as applying  $g_{\text{eqv}}(t)$  to a linear filter<sup>4</sup>, will be considered.

**Traditional Version.** As expressed by (2.10) and illustrated in Figure 2.2, the process of sampling a signal is nonlinear. However, if the signal  $g(t) \leftrightarrow G(f)$  being sampled is characterized by *Nyquist's Sampling Criteria*,

$$G(f) = 0$$

for  $|f| > f_s/2$  (2.11)

it follows that the sampled signal  $g_d(k) \leftrightarrow G_d(f)$  is equivalent to  $g(t) \leftrightarrow G(f)$  in the Nyquist Range  $|f| < f_s/2$ . In other words, by filtering  $g_{\text{eqv}}(t)$  with a linear filter having the transfer function H(f)

$$H(f) = \begin{cases} 1 & \text{for } |f| < f_s/2 \\ 0 & \text{for } |f| > f_s/2 \end{cases}$$

(2.12)

the result will be g(t).

$<sup>^4</sup>g_{\rm eqv}(t)$  was defined by Equation (2.9).

*Nyquist's Sampling Theorem* simply states that a signal, which fulfills Nyquist's Sampling Criteria, can be ideally reconstructed from its sampled sequence.

### 2.2.5 Aliasing

If a signal is sampled at a sampling frequency  $f_s$ , which does not fulfill Nyquist's Sampling Criteria (2.11), *aliasing* will occur. Aliasing simply means that the individual terms in the sum described by Equation (2.10) overlap, i.e., that two terms both are non-zero at some frequency  $f_0$ . Figure 2.2 illustrates a situation in which significant aliasing takes place at frequencies around  $f_s/2 + nf_s$ ,  $n \in \mathbb{Z}$ .

Aliasing can sometimes be allowed. For example, if a signal only needs to be reconstructed in an application's signal band, it is sufficient to require that aliasing does not take place at signal-band frequencies.

**Modified Sampling Criteria.** For an application which is characterized by the signal band,  $|f| < f_b < f_s/2$ , the signal-band part of a signal g(t) can be ideally reconstructed from the sequence  $g_l(k)$  sampled from g(t) at the sampling frequency  $f_s$ , if and only if

$$G(f) = 0 \quad \text{for} \quad |f| > f_s - f_b$$

(2.13)

For the maximum signal-band width ( $f_b = f_s/2$ ), this modified sampling criteria is equivalent to Nyquist's Sampling Criteria.

## 2.3 Estimation of a Signal's Fourier Spectrum

The mathematical definition of the Fourier Transformation, Equation (2.2), is used mainly for theoretical derivations. In practice, a method is needed to estimate the Fourier spectrum G(f) of a signal g(t), which has been obtained by simulations or through experiments. The main incentive to discuss this method in some detail is that it is used extensively to evaluate the performance of data converters. For a more detailed and coherent discussion of this topic, the reader is referred to [21] and [22].

### 2.3.1 Estimation Based on a Finite-Duration Signal

Obviously, it will generally be impossible to calculate the actual Fourier Transformation (2.2), because any estimation process can only be based on finite-duration signals. Only in special cases, e.g. when the signal is known to be periodic and an exact representation of a period of the signal is available, can the Fourier transform be calculated accurately. In the following, it will be assumed that  $G(f) \leftrightarrow g(t)$  will be estimated on the basis of g(t) known for  $|t| < T_{\rm obs}/2$ , where  $T_{\rm obs}$  is some chosen observation time.

A typical way to estimate G(f) is to calculate  $G_{\text{obs}}(f) \leftrightarrow g_{\text{obs}}(t)$ , where  $g_{\text{obs}}(t)$  is defined as  $g_{\text{obs}}(t) = w_{\text{sq}}(t)g(t)$  and  $w_{\text{sq}}(t)$  is the chosen *time window*, which in the following is defined as

$$w_{\rm sq}(t) = \begin{cases} 1 & \text{for } |t| < T_{\rm obs}/2 \\ 0 & \text{otherwise} \end{cases}$$

(2.14)

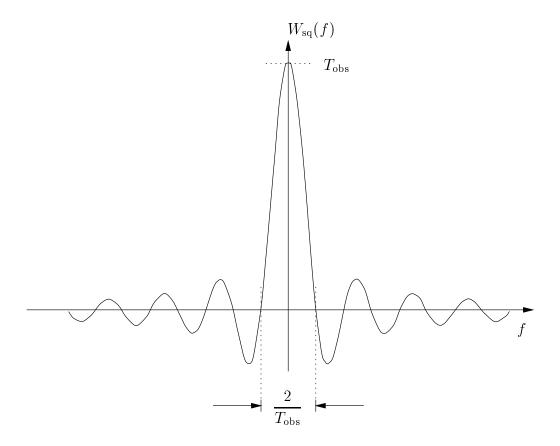

The feasibility of this technique follows from calculating the Fourier transform  $W_{\!sq}(f)$  of  $w_{\!sq}(t)$  as

$$W_{\rm sq}(f) = \int_{-T_{\rm obs}/2}^{T_{\rm obs}/2} e^{-j2\pi f t} dt = T_{\rm obs} \frac{\sin(\pi f T_{\rm obs})}{\pi f T_{\rm obs}}$$

(2.15)

The Fourier transform  $W_{sq}(f)$  is illustrated in Figure 2.3, where it can be seen that the window's *main lobe* is twice as wide as the reciprocal of the observation time, and as high as the observation time.

Equation (2.7) implies that

$$G_{\text{obs}}(f) = G(f) * W_{\text{sq}}(f)$$

(2.16)

This agrees with the observation that  $W_{\rm sq}(f)$  is an impulse approximation when  $T_{\rm obs} \to \infty$ , in which case  $G(f) = G_{\rm obs}(f)$ . It is, however, more important to consider the case where  $T_{\rm obs}$  is finite.

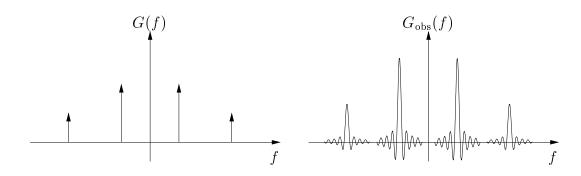

**Properties of Finite-Duration Estimates.** Figure 2.4 shows on the left the Fourier spectrum G(f) of a two-tone periodic signal, and to the right the Fourier spectrum  $G_{obs}(f)$  of the observed signal. Notice that  $G_{obs}(f)$  can easily be predicted on the basis of the Fourier transform G(f), Figure 2.3, and Equation (2.16).

Figure 2.3: The Fourier transform of the rectangular window  $u_{\rm sq}(t)$ .

Figure 2.4: The actual and the observed frequency spectrum of a two-tone periodic signal.

Clearly, when estimating a signal's Fourier spectrum on the basis of a finite-duration representation, the energy located at any one frequency, say  $f_0$ , will be smeared over a range of frequencies in the neighborhood of  $f_0$ . This effect is called *spectral leakage*.

The range of frequencies to which the energy leaks is in principle infinitely wide. However, the width of the frequency range, in which any given fraction (say 99.9%) of the energy is represented, will be inversely proportional to the duration  $T_{\rm obs}$  of the observed signal. The width of the window's  $W_{\rm sq}(f)$  main lobe will in the following be called the window's *spectral aperture*. Notice that the spectral composition of a signal can be estimated with any accuracy, simply by using a sufficiently long observation time  $T_{\rm obs}$ .

In the example illustrated in Figure 2.4,  $G_{\text{obs}}(f)$  represents only a fraction of the energy of G(f); this is a simple implication of g(t) being periodic, and hence of infinite energy, whereas  $g_{\text{obs}}(t)$  is of finite duration and energy.

### 2.3.2 Estimation Based on Assumed Periodicity

All real-world analog signals are continuous and of finite duration, and hence they can be analyzed using the basic Fourier transform without encountering any convergence problems. However, it is often preferable to estimate a signal's spectral composition in terms of power rather than energy. One reason is that the typical test setup will evaluate a system's steady-state response to an input that is periodic in the observation period. In that case, the observed signal will supposedly consist of a periodic deterministic component (the signal) and a stationary stochastic component (noise).

The following is based on the fundamental assumption that the analyzed signal g(t) can be approximated by an periodic extension  $g_{per}(t)$  of the observed signal  $g_{obs}(t)$

$$g_{\text{per}}(t) = \sum_{n=-\infty}^{\infty} g_{\text{obs}}(t - nT_{\text{obs}}) = \sum_{n=-\infty}^{\infty} g(t - nT_{\text{obs}}) w_{\text{sq}}(t - nT_{\text{obs}})$$

(2.17)

Assuming that  $T_{\rm obs}$  spans exactly an integer number of periods, the deterministic component will be represented with great accuracy, but it should be obvious that a periodic extension of a stochastic component will not represent the actual stochastic process.

A stationary stochastic process is best described by its autocorrelation function and the Fourier transform thereof, i.e., the *Spectral Power Density* (SPD) (cf. [23]); but in practice, the noise signal's SPD can be estimated only on the basis of a periodic extension of an observed finite-duration sequence.

In the following, the *average value* shall refer to averaging in the period of time in which the considered signal is observed.

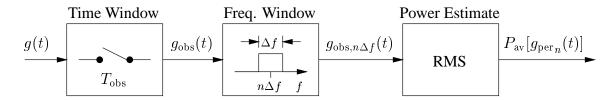

**The Band-Pass-Filter Method.** Figure 2.5 shows the fundamental elements of the Band-Pass-Filter (BPF) method.

Figure 2.5: Fundamental steps in the Band-Pass-Filter (BPF) method.

Using Parseval's Theorem (2.5) and the definition of the time window (2.14), it follows that the average power of the periodic extension  $g_{\text{per}}(t)$  of  $g_{\text{obs}}(t)$  can be calculated as

$$P_{\rm av}[g_{\rm per}(t)] = \frac{1}{T_{\rm obs}} \int_{-\infty}^{\infty} |G_{\rm obs}(f)|^2 df$$

(2.18)

The BPF method uses a tunable band-pass filter to isolate individual parts of the frequency spectrum of  $G_{\text{obs}}(f)$ . For simplicity, the bandpass filter is assumed to be ideal with a single-sided tunable center frequency of  $n\Delta f$  and a bandwidth of  $\Delta f$ . Equation (2.18) can, therefore, be written in the form

$$P_{\text{av}}[g_{\text{per}}(t)] = \frac{1}{T_{\text{obs}}} \sum_{n=-\infty}^{\infty} \left[ \int_{\Delta f(n-0.5)}^{\Delta f(n+0.5)} |G_{\text{obs}}(f)|^2 df \right]$$

$$= \frac{1}{T_{\text{obs}}} \sum_{n=-\infty}^{\infty} \left[ \int_{-\infty}^{\infty} |G_{\text{obs},n\Delta f}(f)|^2 df \right]$$

(2.19)

Using Parseval's Theorem (2.5) and (2.19), it follows that  $g_{per}(t)$  thereby is separated in terms of power

$$P_{\text{av}}[g_{\text{per}}(t)] = \frac{1}{T_{\text{obs}}} \sum_{n=-\infty}^{\infty} \left[ \int_{-\infty}^{\infty} g_{\text{obs},n\Delta f}(t)^2 dt \right]$$

$$= \sum_{n=-\infty}^{\infty} P_{\text{av}}[g_{\text{obs},n\Delta f}(t)]$$

(2.20)

When estimating a noise signal, it makes the most sense to assume that  $|G_{\rm obs}(f)|$  is constant in the narrow frequency ranges:  $(n-0.5)\Delta f < f < (n+0.5)\Delta f$ , and hence that  $|G_{\rm obs}(f)|$  should be estimated by

$$|G_{\text{obs}}(f)| = \sqrt{\frac{1}{\Delta f}} \int_{-\infty}^{\infty} g_{\text{obs},n\Delta f}(t)^{2} dt$$

$$= \sqrt{T_{\text{obs}}} \sqrt{\frac{P_{\text{av}}[g_{\text{obs},n\Delta f}(t)]}{\Delta f}} \quad \text{for} \quad |f - n\Delta f| < 0.5\Delta f$$

(2.21)

However, when estimating a deterministic and assumed periodic signal component, it makes more sense to approximate the estimated power by assuming a tone at  $n\Delta f$ , and hence that  $|G_{per}(f)|$  should be estimated as

$$|G_{\text{per}}(f)| = \delta(f - n\Delta f) \frac{\sqrt{P_{\text{av}}[g_{\text{obs},n\Delta f}(t)]}}{2} \quad \text{for} \quad |f - n\Delta f| < 0.5\Delta f$$

(2.22)

Using equations (2.15) and (2.16), it follows that the respective portion of  $|G_{\rm obs}(f)|$  can be estimated as

$$|G_{\text{obs}}(f)|_{n\Delta f} = W_{\text{sq}}(f - n\Delta f) \frac{\sqrt{P_{\text{av}}[g_{\text{obs},n\Delta f}(t)]}}{2}$$

(2.23)

For real-world implementations of the BPF method, the window's spectral aperture will typically be much smaller than the band-pass filter's band-width, and hence the individual terms of (2.23) will usually not overlap significantly.

#### 2.3.3 The Discrete Fourier Transformation

The Discrete Fourier Transformation (DFT) is, in principle, just an implementation of the BPF method. Hence, all the above comments on the assumed periodicity etc. also apply to the DFT. The DFT is a numeric technique, which is implemented using DSP<sup>5</sup>, therefore it is applied only to digital signals. Thus, to obtain an estimate of the Fourier spectrum of a continuous-time signal, it must first be sampled according to Nyquist's Criteria, Equation (2.11), to avoid aliasing. Because the DFT can be implemented with arbitrary accuracy, both the real and the imaginary part of the Fourier spectrum can be estimated.

Using the DFT is the natural approach in a simulation environment, but it can also be used for laboratory measurements<sup>6</sup>.

Fundamental Properties of the DFT. The DFT is calculated on the basis of a finite sequence of N samples, which are assumed to result from a uniform sampling with the sampling period  $T_s$ . The observation period  $T_{obs}$  is therefore

$$T_{\rm obs} = NT_s \tag{2.24}$$

The DFT can be considered to be an implementation of the BPF method using an array of N bandpass filters with center frequencies  $\frac{n}{N}f_s$ ,  $n \in \{0, 1, 2, ..., (N-1)\}$ , each with a bandwidth of  $f_s/N$ . Because the analyzed signal g(k) is sampled, the Fourier spectrum will be periodic with period  $f_s$ , and hence the DFT provides an estimate of the entire Fourier spectrum.

As discussed with respect to the BPF method, it is a choice whether the estimated power in a given frequency range is assumed to be equally distributed at all frequencies in the frequency range, or concentrated at a single frequency in the range. The DFT cannot possibly make an intelligent choice, and hence it always assumes that the power is located only at the band-pass filter's center frequencies (which in the following will be called the *fundamental frequencies*). Indeed, this is the correct choice if the analyzed signal is periodic with the period<sup>7</sup>  $T_{\rm obs}$ . In other words, the DFT assumes that g(k) can be

<sup>&</sup>lt;sup>5</sup>The DFT is available in many dedicated software packages, such as MATLAB.

<sup>&</sup>lt;sup>6</sup>Measurement equipment which is based on the DFT, however, requires a dedicated highly-accurate ADC [24].

<sup>&</sup>lt;sup>7</sup>It does not have to be the shortest period.

written in the form

$$g_{\text{obs}}(k) = \sum_{n=0}^{N-1} c_n e^{j2\pi (f_s n/N)k}$$

$$= \sum_{n=0}^{N-1} a_n \cos(2\pi (f_s n/N)k) + jb_n \sin(2\pi (f_s n/N)k)$$

(2.25)

The vector DFT(n) is simply the N complex coefficients in

$$DFT(n) = c_{n+1}, \ n \in \{1, 2, 3, \dots, N\}$$

(2.26)

Windowing. The DFT's method of allocating the estimated power is only correct if the analyzed signal g(k) is periodic with the period  $T_{\rm obs}$ . In a simulation environment, it is often possible to assure that the signal component of the analyzed signal fulfills this requirement, but errors that are not in harmonic relation to the signal component, such as the quantization "noise" in delta-sigma modulators, will usually not be periodic with period  $T_{\rm obs}$ . As for the BPF method, spectral leakage will occur if the periodicity requirement is not fulfilled.

The Fourier transform  $W_{\rm sq}(f)$  of the basic rectangular time window (2.14) was shown in Figure 2.3. The zero crossings of this transform are equidistant with the same distance as the spacing between the DFT's fundamental frequencies. An implication of this property is that  $G_{\rm obs}(f)$  in (2.16) equals the analyzed signal's Fourier spectrum G(f) at the frequencies of interest if, but only if, g(k) is periodic with period  $T_{\rm obs}$ . In other words, assuming periodicity, spectral leakage will not occur in the DFT. However, if g(k) is not periodic with period  $T_{\rm obs}$ , spectral leakage will occur, and it may cause very misleading results, especially when using the DFT to estimate the Fourier spectrum of a signal with substantial out-of-band power<sup>8</sup>.

Fortunately, it is fairly simple to avoid the deleterious effects of spectral leakage. The technique is to avoid substantial areas of the side lobes in the time window's Fourier transformed (see Figure 2.3). Side-lobe suppression can be obtained by scaling the time window's coefficients (2.14), such that, even

<sup>&</sup>lt;sup>8</sup>This is especially important for single-bit delta-sigma modulators where the out-of-band power in general will be greater than the signal power.

in the lack of periodicity, the periodic extension of the observed windowed representation of the analyzed *continuous-time* signal  $g_{per}(t)$  is continuous and has continuous derivatives. An outstanding and comprehensive tutorial on windowing, including the theory and the advantages and disadvantages of various windows, is provided by Harris [22].

All DFTs that are presented in the following have utilized the Hanning Window. The Hanning Window is characterized by a fairly narrow main lobe, a good suppression of spectral components away from the main lobe, and a worst-case *processing loss* of approximately 3 dB. A window's processing loss is comparable to the noise factor of an analog circuit. The results presented in this thesis have *not* been corrected for the window's processing loss, therefore all the results may be up to 3 dB on the pessimistic side. Power located at any one of the fundamental frequencies will leak to the two neighboring fundamental frequencies. Hence, the power of a sinusoid signal must be estimated as the power represented by three coefficients in DFT(n).

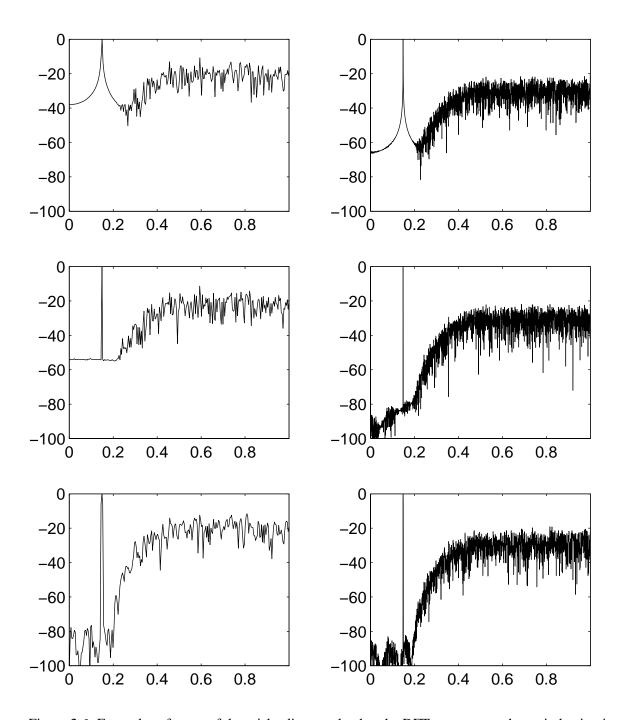

An Example of Windowing. Figure 2.6 shows six DFTs, which are all calculated from the same signal provided by an ideal four-bit delta-sigma modulator. Each of the plots show the DFT coefficients in dB versus frequency normalized with respect to  $f_s/2$ . The estimated signal consists of a signal component, a sinusoid at the normalized frequency 0.16; and a pseudo-stochastic component, the quantization noise that supposedly has very little energy in the signal band, i.e. in the normalized frequency range from 0 to 0.2.

The DFTs in the left-hand column are based on 512 samples, whereas the DFTs in the right-hand column are based on 4096 samples. Hence, the bandwidth of the longer DFTs band-pass filters is eight times smaller than the bandwidth of the short DFTs band-pass filters. This property is reflected by the DFT coefficients that represent the noise components, e.g., at the normalized frequencies from 0.4 to 1, which are 9 dB lower for the longer DFTs. The coefficients of the DFTs that represent the signal component are, however, unaffected by the length of the DFT, because the energy is concentrated at a single frequency, which will be part of only one band-pass filter's pass band. Hence, the modulator's signal-to-noise ratio (SNR) cannot be estimated as "the vertical distance between the signal bin and the noise floor," which is

<sup>&</sup>lt;sup>9</sup>When not encountering spectral leakage.

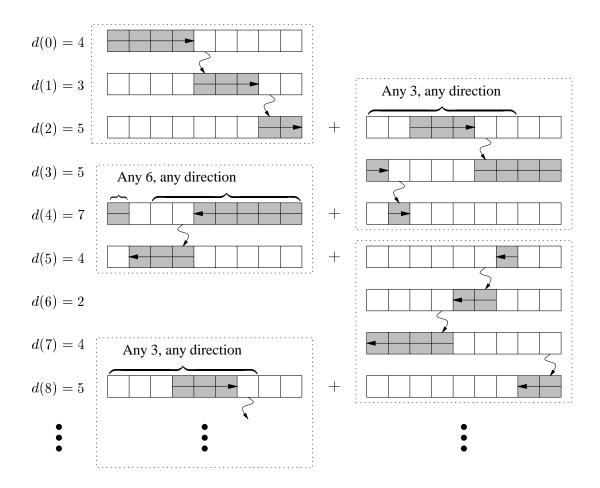

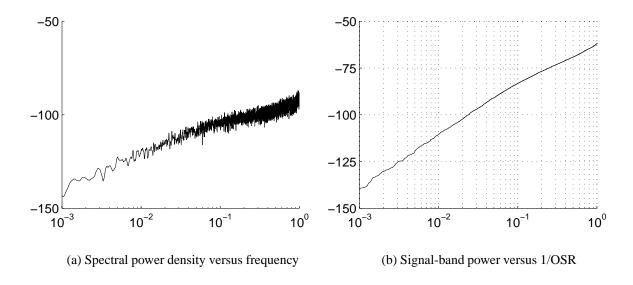

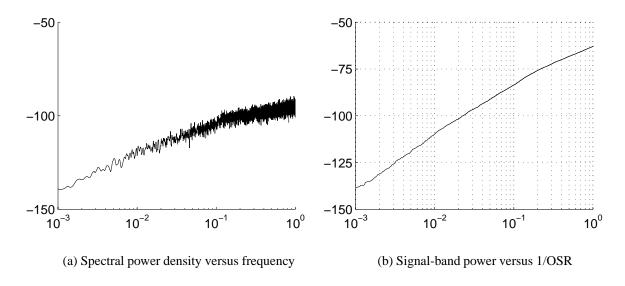

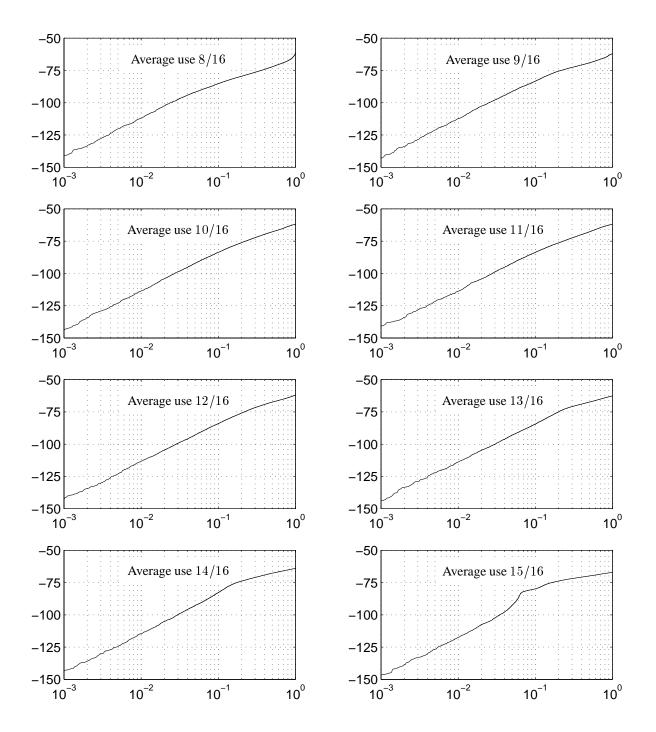

Figure 2.6: Examples of some of the misleading results that the DFT may cause when windowing is not used correctly. The two lower plots are "correct."

a common misconception.